Uartcr, Uartfr – Siemens ERTEC200 User Manual

Page 52

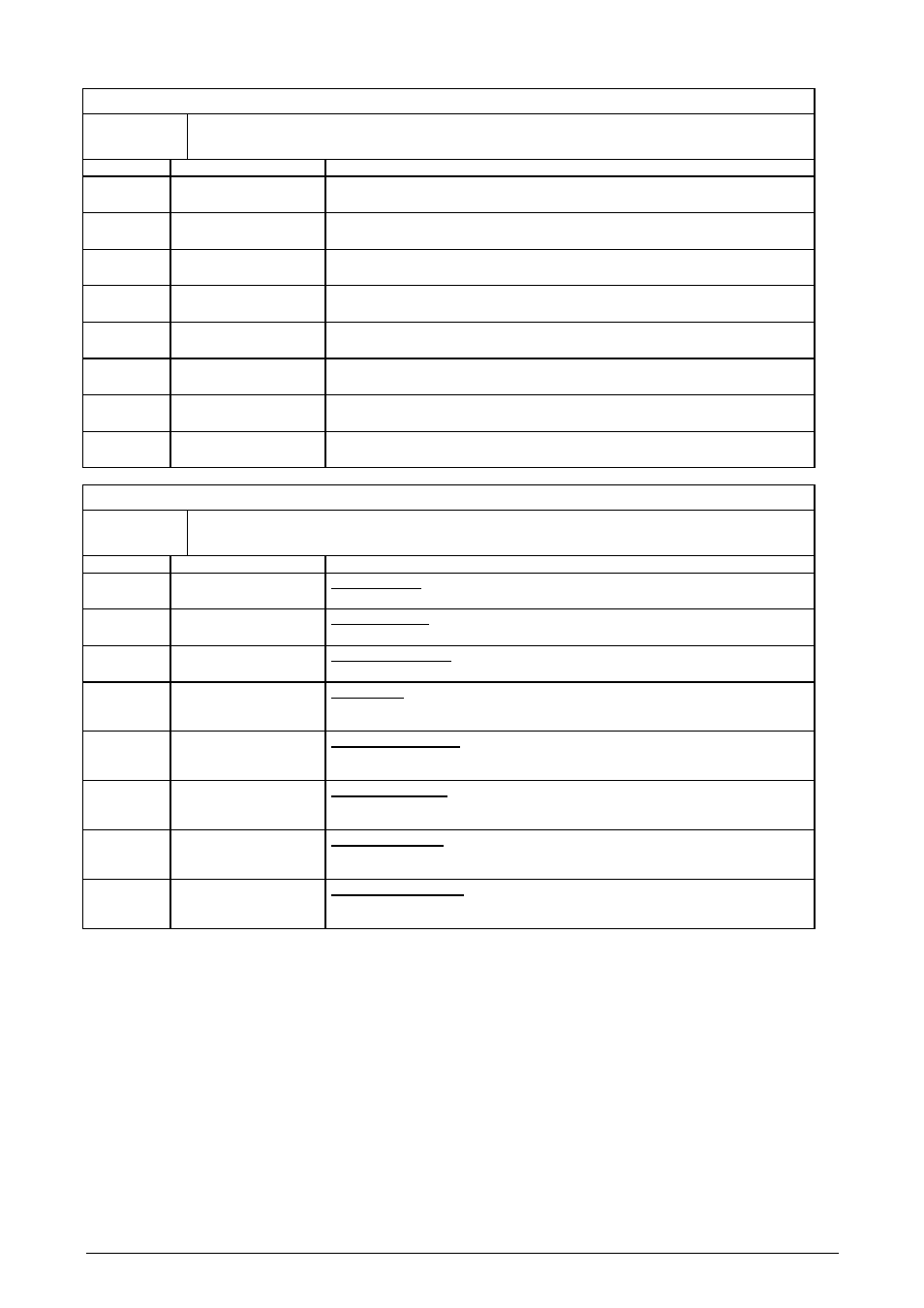

UARTCR

R/W Addr.: 0x4000_2314 Default: 0x00

Description

UART control registers

Bit No.

Name

Description

0

UARTEN

UART Enable = 1 UART sending/receiving of data is enabled

1

SIREN

SIR enable = 1 IrDA SIR Endec is enabled. The bit can only be changed if

UARTEN = 1

2

SIRLP

IrDA SIR Low power mode

3

MSIE

Modem status interrupt enable = 1 Interrupt is enabled

4

RIE

Receive interrupt enable = 1 Receive interrupt is enabled

5

TIE

Transmit interrupt enable = 1 Transmit interrupt is enabled

6

RTIE

Receive timeout interrupt enable = 1 Receive timeout interrupt is enabled

7

LBE

Loop back enable

UARTFR

R Addr.: 0x4000_2318 Default: 0x9-

Description

UART flag registers

Bit No.

Name

Description

0

CTS

Clear To Send This bit is the inverse signal of UART input CTS.

1 DSR

Data Set Ready This bit is the inverse signal of UART input DSR.

2 DCD

Data Carrier Detect This bit is the inverse signal of UART input DCD.

3 BUSY

UART Busy The bit is set if send data are in progress or if the Transmit FIFO

is not empty.

4 RXFE

Receive

FIFO

Empty = 1 if

FIFO is disabled and Receive holding register is empty

FIFO is disabled and Receive FIFO buffer is empty

5 TXFF

Transmit

FIFO

Full = 1 if

FIFO is disabled and Transmit holding register is full

FIFO is enabled and Transmit FIFO buffer is full

6

RXFF

Receive FIFO Full = 1 if

FIFO is disabled and Receive holding register is full

FIFO is enabled and Receive FIFO buffer is full

7 TXFE

Transmit

FIFO

Empty = 1 if

FIFO is disabled and Transmit holding register is empty

FIFO is enabled and Transmit FIFO buffer is empty

Copyright © Siemens AG 2007. All rights reserved.

52

ERTEC 200 Manual

Technical data subject to change Version 1.1.0