Icu register description, Table 4: overview of interrupt control register – Siemens ERTEC200 User Manual

Page 28

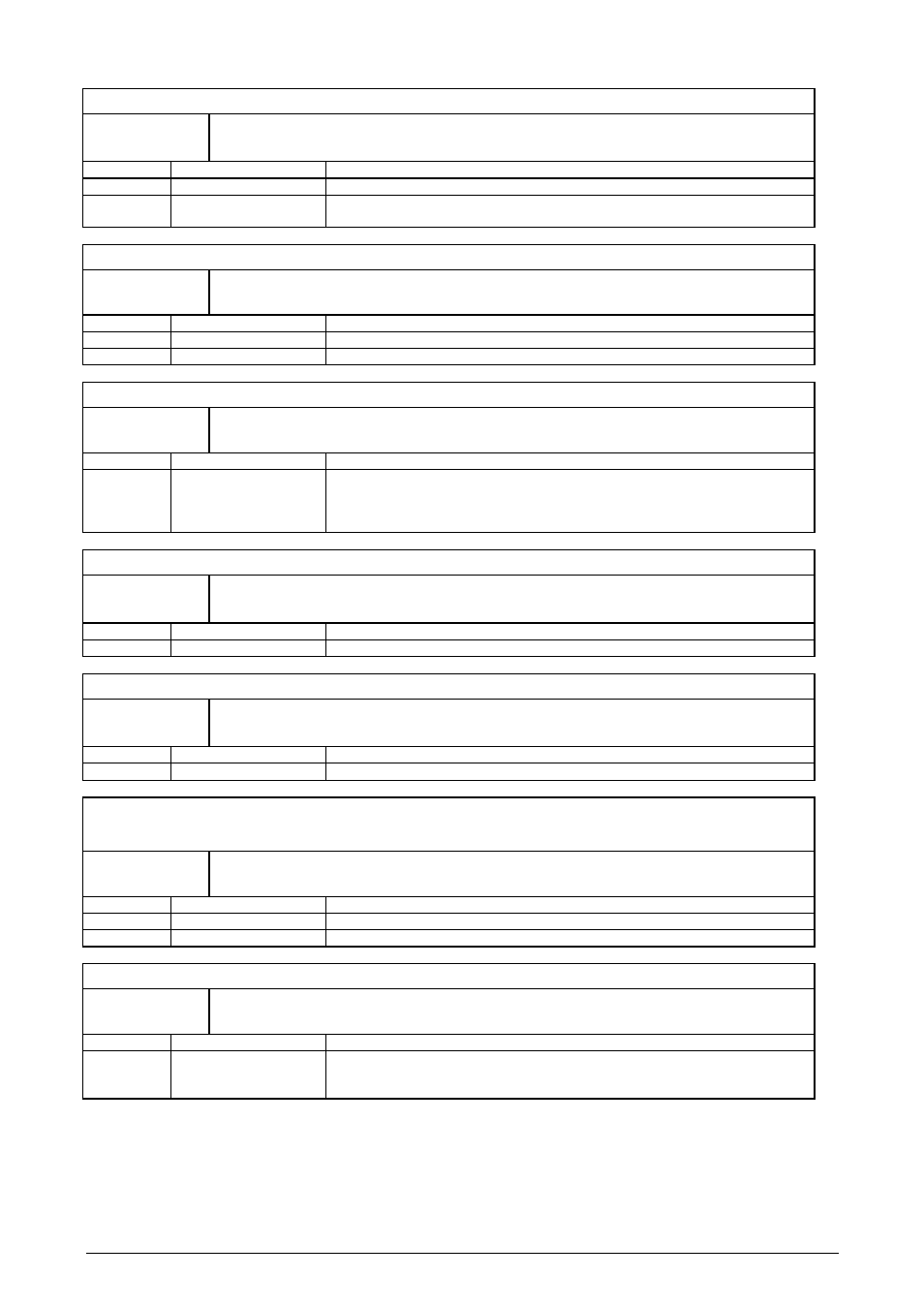

FIQACK

R

Addr.: 0x5000_0018 Default:

0xFFFF_FFFF

Description

Fast interrupt vector register with FIQ acknowledge

Confirmation of fast interrupt request by reading the associated

interrupt vector

Bit No.

Name

Description

2 – 0

FIVEC

Binary code of FIQ number

31 – 3

Vector ID

Valid FIQ vector: always ‘1’.

Default vector: always ‘1’ (also bits 2 – 0).

IRCLVEC

W

Addr.: 0x5000_001C

Default: ----

Description

Interrupt request clear vector

Immediate deletion of an interrupt request in the interrupt request register

Bit No.

Name

Description

3 – 0

IRCLVEC

Binary code of the input number of the request to be deleted

7 unused

MASKALL

R/W

Addr.: 0x5000_0020

Default: '1'

Description

Mask all Interrupts

Global disable for all IRQ interrupt inputs

Bit No.

Name

Description

0

MASKALL

'0' = Enable all non-masked IRQ interrupt inputs

(consideration given to set mask bits)

'1' = Global disable for all IRQ interrupt inputs

(independent of the interrupt mask)

IRQEND

W

Addr.: 0x5000_0024

Default: ----

Description End-of-interrupt

(IRQ)

Communicates to the IRQ interrupt controller the completion of the interrupt service routine

associated with the current request

Bit No.

Name

Description

Not

used

FIQEND

W

Addr.: 0x5000_0028

Default: ----

Description End-of-interrupt

(FIQ)

Communicates to the FIQ interrupt controller the completion of the interrupt service routine

associated with the fast interrupt request

Bit No.

Name

Description

Not

used

FIQPR0

R/W

Addr.: 0x5000_002C

Default: 0x0000_0007

…

….

FIQPR7

R/W

Addr.: 0x5000_0048

Default: 0x0000_0007

Description

FIQ priority registers

Priority of the fast interrupt request at input FIQ0 to FIQ7 of the FIQ interrupt controller

Bit No.

Name

Description

2 – 0

FIQPR0 to 7

Binary code of the priority

7 – 3

Not used

FIQISR

R

Addr.: 0x5000_004C

Default: 0x0000_0000

Description

FIQ in-service register

Indication of the fast interrupt requests confirmed by the CPU

Bit No.

Name

Description

7 – 0

FIQISR

Inputs 0 to 7 of the FIQ interrupt controller

'0' = Fast interrupt request not confirmed

'1' = Fast interrupt request has been confirmed

Copyright © Siemens AG 2007. All rights reserved.

28

ERTEC 200 Manual

Technical data subject to change Version 1.1.0