Address assignment of lbu registers, Lbu register description, Host interrupt handling – Siemens ERTEC200 User Manual

Page 83: Lbu_p0_rg_l, Lbu_p1_rg_l, Lbu_p2_rg_l, Lbu_p3_rg_l, 7 address assignment of lbu registers, 8 lbu register description

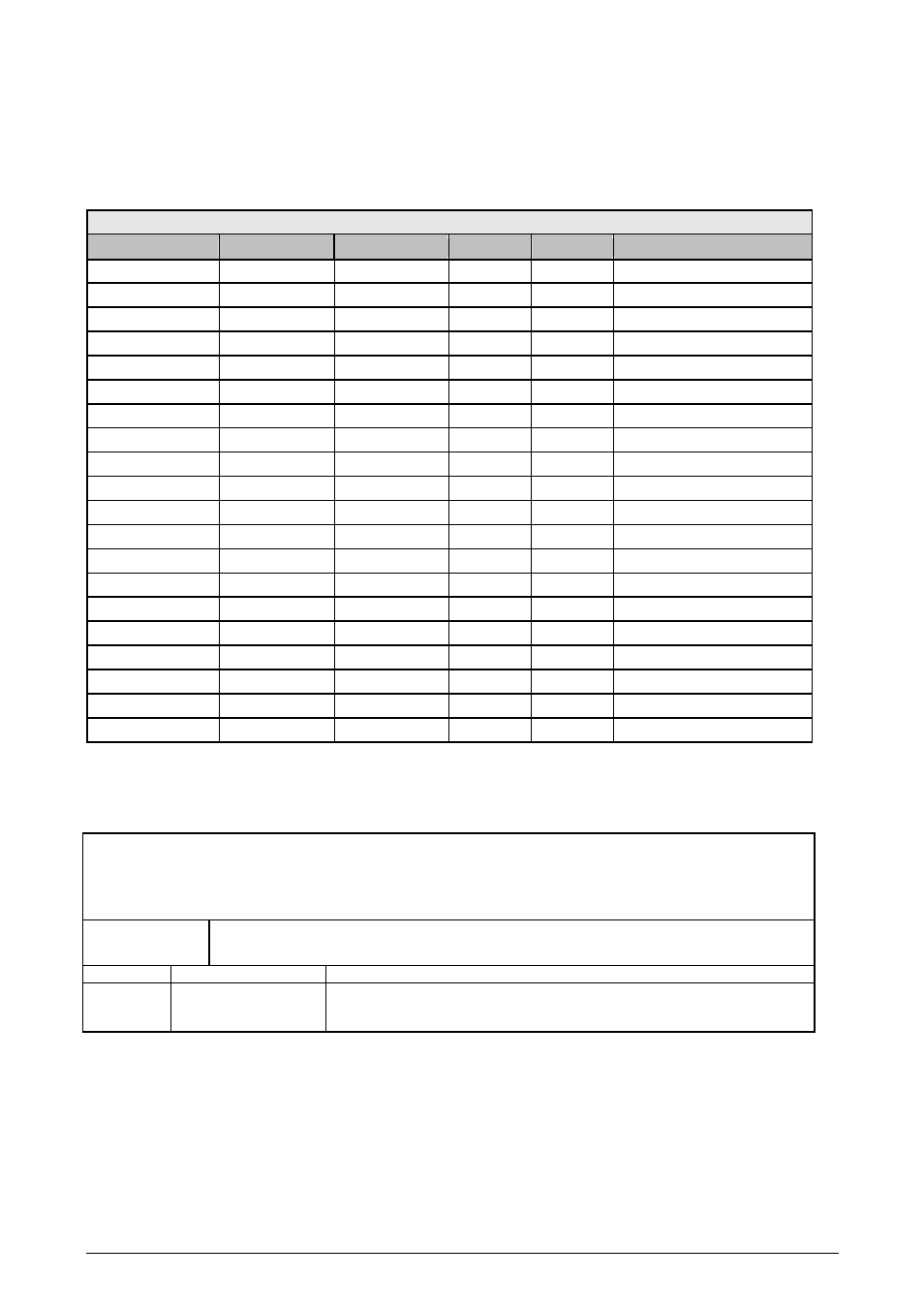

7.7 Address Assignment of LBU Registers

The LBU registers are 16 bits in width. These registers can only be written to with words. The LBU paging configuration

registers are addressed via the "LBU_CS_R_N” input.

LBU

Register Name Offset Address Address Area

Access

Default

Description

LBU_P0_RG_L

0x0000

2 bytes

W/R

0x0000

LBU pagex range register 0 Low

LBU_P0_RG_H

0x0002

2 bytes

W/R

0x0001

LBU pagex range register 0 High

LBU_P0_OF_L

0x0004

2 bytes

W/R

0x0000

LBU pagex offset register 0 Low

LBU_P0_OF_H

0x0006

2 bytes

W/R

0x1010

LBU pagex offset register 0 High

LBU_P0_CFG

0x0008

2 bytes

W/R

0x0000

LBU configuration register 0

LBU_P1_RG_L

0x0010

2 bytes

W/R

0x0000

LBU pagex range register 1 Low

LBU_P1_RG_H

0x0012

2 bytes

W/R

0x0010

LBU pagex range register 1 High

LBU_P1_OF_L

0x0014

2 bytes

W/R

0x0000

LBU pagex offset register 1 Low

LBU_P1_OF_H

0x0016

2 bytes

W/R

0x1000

LBU pagex offset register 1 High

LBU_P1_CFG

0x0018

2 bytes

W/R

0x0001

LBU configuration register 1

LBU_P2_RG_L

0x0020

2 bytes

W/R

0x0000

LBU pagex range register 2 Low

LBU_P2_RG_H

0x0022

2 bytes

W/R

0x0020

LBU pagex range register 2 High

LBU_P2_OF_L

0x0024

2 bytes

W/R

0x0000

LBU pagex offset register 2 Low

LBU_P2_OF_H

0x0026

2 bytes

W/R

0x3000

LBU pagex offset register 2 High

LBU_P2_CFG

0x0028

2 bytes

W/R

0x0000

LBU configuration register 2

LBU_P3_RG_L

0x0030

2 bytes

W/R

0x0800

LBU pagex range register 3 Low

LBU_P3_RG_H

0x0032

2 bytes

W/R

0x0000

LBU pagex range register 3 High

LBU_P3_OF_L

0x0034

2 bytes

W/R

0x2000

LBU pagex offset register 3 Low

LBU_P3_OF_H

0x0036

2 bytes

W/R

0x4000

LBU pagex offset register 3 High

LBU_P3_CFG

0x0038

2 bytes

W/R

0x0001

LBU configuration register 3

Table 29: Overview of LBU Registers

7.8 LBU Register Description

LBU_P0_RG_L

W/R Addr.: LBU_CS_R_N+0x00 Default: 0x0000_0000

LBU_P1_RG_L

W/R Addr.: LBU_CS_R_N+0x10 Default: 0x0000_0000

LBU_P2_RG_L

W/R Addr.: LBU_CS_R_N+0x20 Default: 0x0000_0000

LBU_P3_RG_L

W/R Addr.: LBU_CS_R_N+0x30 Default: 0x0000_0800

Description

Low word of LBU Pagex_Range_register

Bit No.

Name

Description

15..0

Lower 16 bits for area setting

15:8 are read/write accessible

7:0 are read-only (value: 00h)

Copyright © Siemens AG 2007. All rights reserved.

83

ERTEC 200 Manual

Technical data subject to change Version 1.1.0