Dma-controller, 8 dma-controller – Siemens ERTEC200 User Manual

Page 85

8 DMA-Controller

The ERTEC 200 has a 1-channel DMA controller. This enables data to be transferred without placing an additional load

on the ARM946E-S. The following data transfers are possible:

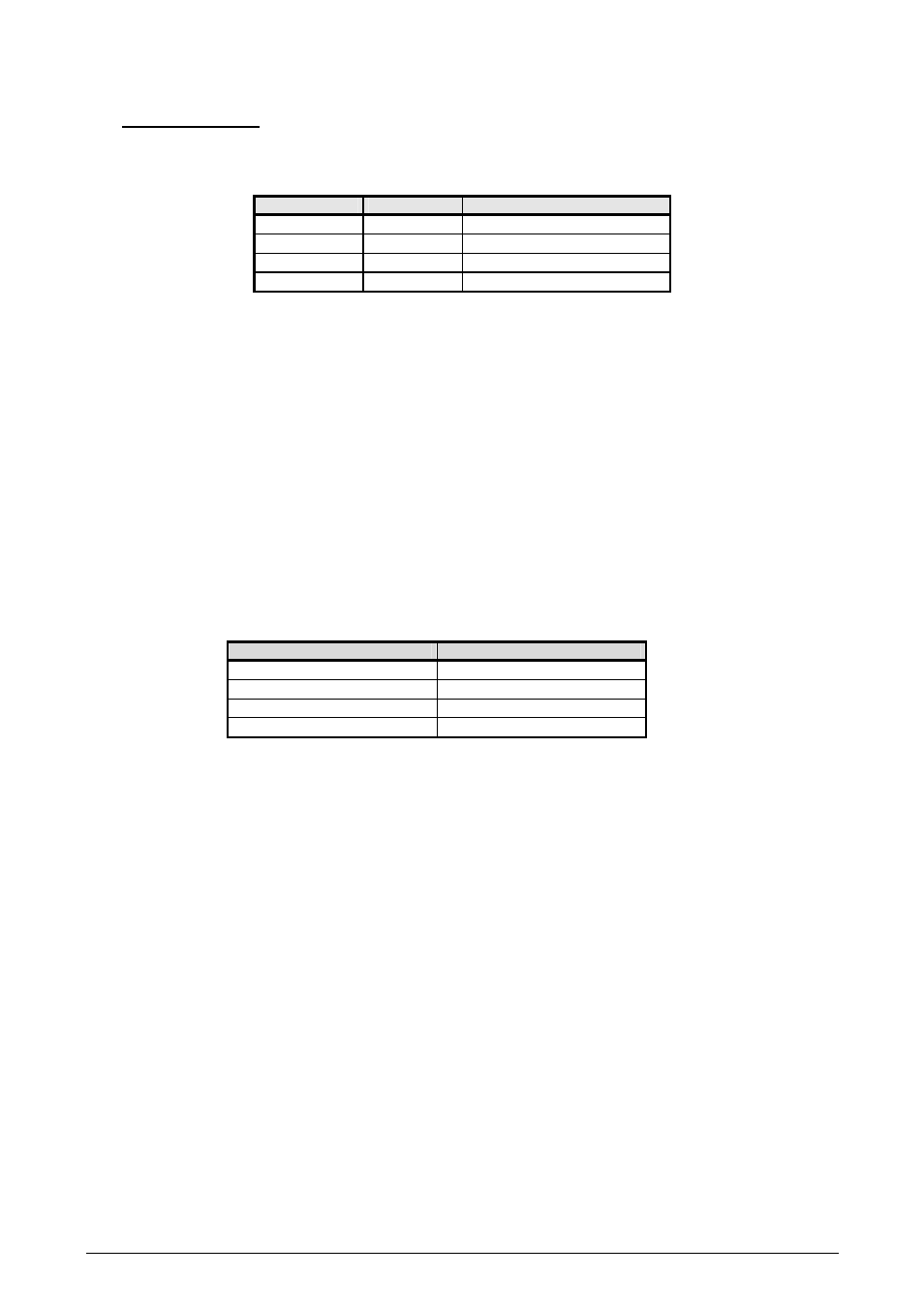

SOURCE

TARGET

SYNCHRONIZATION

Peripheral

(1)

Memory

Source

Memory Peripheral

(1)

Target

Peripheral

(1)

Peripheral

(1)

Source and Target

Memory Memory

None

Table 30: DMA Transfer Modes

Note (1) Due to the single-channel structure, the DMA controller can only service one direction (transmit or receive) in

serial interfaces. In the case of full-duplex operation, the other direction must be processed via software.

Properties of the DMA controller:

•

AHB master interface for the transfer of data

•

AHB slave interface for ARM946E-S access to the DMA register

•

4 request inputs for synchronization of the DMA controller with the SPI or UART I/O

•

Source and destination address must always be 4-byte aligned (bits 1:0 are ignored)

•

A bit width of 8 / 16 / 32 can specified independently for the source or for the target. Here, the bit width can be

smaller than the bit width of source or target.

•

The block size to be transferred is indicated in number of bytes and must be aligned with the set bus width. That

is, if a bus width of 32-bits is assigned as byte count for target or source, only one byte count with 4 bytes

aligned can be used.

• Changed-Address-Mode/Hold-Address-Mode

must be set individually for source and target.

Synchronization signals of UART and SPI for DMA transfers:

SOURCE

DESCRIPTION

SPI1_SSPRXDMA

RX-FIFO not empty

SPI1_SSPTXDMA TX-FIFO

empty

UART_UARTRXINTR UART

Receive

Interrupt

UART_UARTTXINTR

UART Transmit Interrupt

Table 31: I/O Synchronization Signals

Description of the address modes:

•

Change-Address-Mode:

Increments or decrements the target and/or source address after each transfer (byte, 2 bytes, 4 bytes). The

byte counter is incremented or decremented in accordance with the transferred bytes.

•

Hold-Address-Mode:

In this mode, the target or source addressed is fixed.

¾ The DMA transfer can be initiated by the software via a DMA control register or by a hardware signal

Software control:

The transfer can be started or stopped by writing to the Start/Abort DMA configuration register bit.

Hardware control:

The data transfer is controlled by activating the synchronization signal (see table "I/O Synchronization

Signals"). As soon as the sync signal is deactivated, the DMA controller stops the transfer. With the

next activation of the sync signal, the data transfer is resumed by the DMA controller.

¾ When the DMA transfer is complete, a DMA_INTR interrupt takes place. In the case of a transfer to the

UART or SPI, the interrupt takes place after the last byte is transferred.

Copyright © Siemens AG 2007. All rights reserved.

85

ERTEC 200 Manual

Technical data subject to change Version 1.1.0