Watchdog registers, Address assignment of watchdog registers, Watchdog register description – Siemens ERTEC200 User Manual

Page 46: Watchdog timers, Watchdog timer 0, Watchdog timer 1, Watchdog interrupt, Wdout0_n, Wdout1_n, Figure 6: watchdog timing

4.5.6 Watchdog

Registers

The watchdog registers are 32 bits in width. For read/write access of the watchdog registers to be meaningful, a 32-bit

access is required. However, a byte-by-byte write operation is not intercepted by the hardware.

To prevent the watchdog registers from being written to inadvertently, e.g., in the event of an undefined computer crash,

the writable watchdog registers are provided with write protection. The upper 16 bits of the registers are so-called key

bits. In order to write a valid value in the lower 16 bits, the key bits must be set to 0x 9876 yyyy (yyyy is the 16-bit value

to be written).

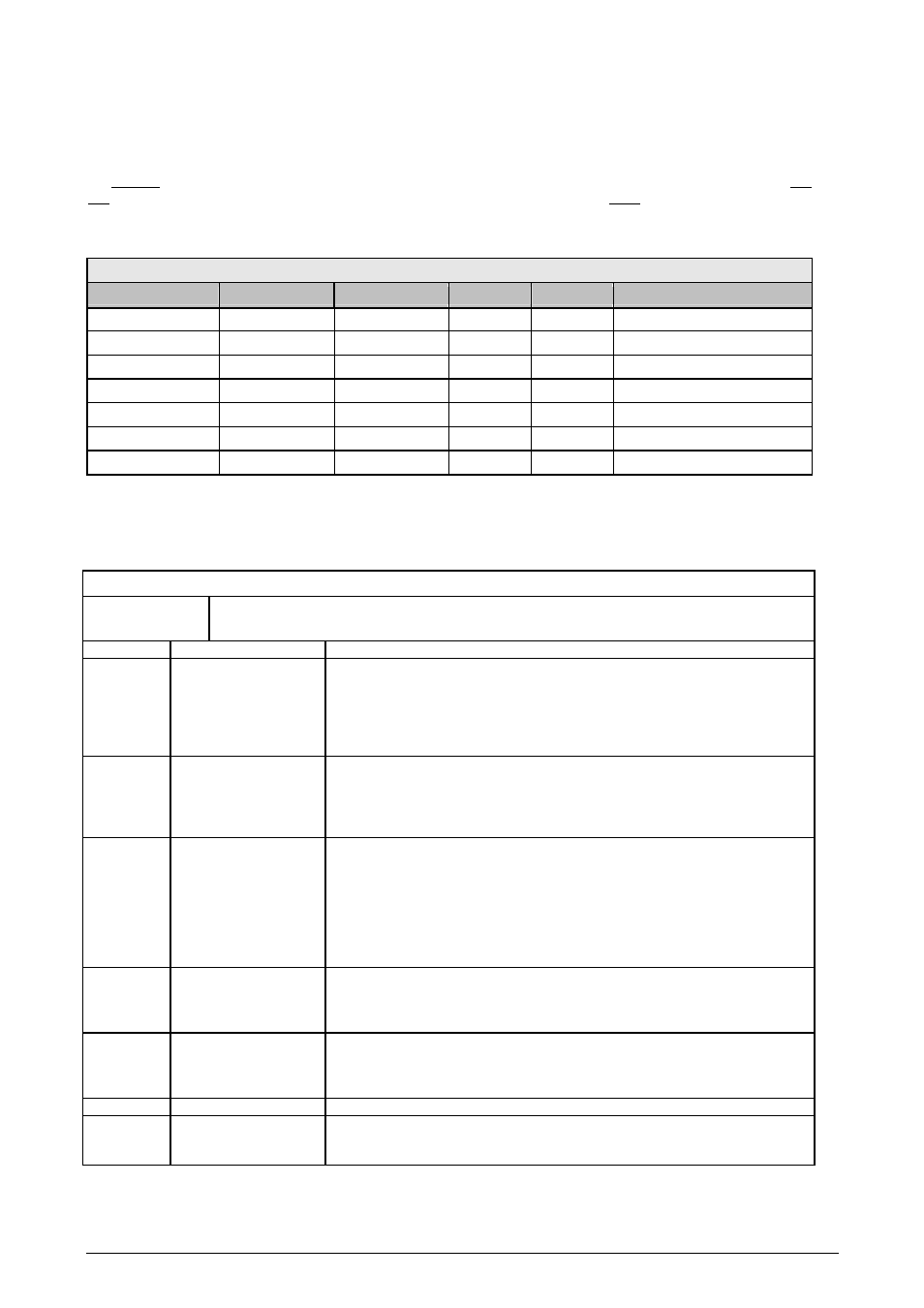

4.5.7

Address Assignment of Watchdog Registers

Watchdog

(Base Address 0x4000_2100)

Register Name

Offset Address

Address Area

Access

Default

Description

CTRL/STATUS

0x0000

4 bytes

R/W

0x00000000

Control/status register WD

RELD0_LOW

0x0004

4 bytes

R/W

0x0000FFFF

Reload register 0_Low Bits 0-15

RELD0_HIGH

0x0008

4 bytes

R/W

0x0000FFFF

Reload register 0_High Bits 16-31

RELD1_LOW

0x000C

4 bytes

R/W

0x0000FFFF

Reload register 1_Low Bits 4-19

RELD1_HIGH

0x0010

4 bytes

R/W

0x0000FFFF

Reload register 1_High Bits 20-35

WDOG0

0x0014

4 bytes

R

0xFFFFFFFF

Watchdog timer 0 value register

WDOG1

0x0018

4 bytes

R

0xFFFFFFFF

Watchdog timer 1 value register

Table 12: Overview of WD Registers

4.5.8 Watchdog

Register

Description

CTRL/STATUS

R/W

Addr.: 0x4000_2100 Default: 0x0000_0000

Description Control/status

register Configuration and control bits for the watchdog.

Bit No.

Name

Description

0

Run/xStop_V0

Enable/disable watchdog counter 0:

0: Watchdog counter 0 disabled

1: Watchdog counter 0 enabled

Note: If this bit = 0, the WDOUT0_n output of the ERTEC 200 is active (0),

the interrupt of the watchdog (WDINT) is “0”, and the status bit of counter 0

(Bit 3) is “0”.

1

Run/xStop_Z1

Enable/disable watchdog counter 1:

0: Watchdog counter 1 disabled

1: Watchdog counter 1 enabled

Note: If this bit = 0, the WDOUT1_N output of the ERTEC 200 is passive (1)

and the status bit of counter 1 (Bit 4) is “0”.

2

Load(Trigger)

Watchdog trigger (load watchdog counters 0 and 1 with the value of the

effect at the instant of writing.

the watchdog counter; a

unters.

reload registers):

0: Do not trigger watchdog

1: Trigger watchdog

While this bit can be read back, it only has an

Writing a value of 1 to this bit is sufficient to trigger

0/1 edge is not needed.

The trigger signal acts on both watchdog co

3

Status_Counter 0

Watchdog status counter 0 (writing is ignored):

0: Watchdog counter 0 has not expired

1: Watchdog counter 0 has expired

Note: This bit can only be read as ‘1’ if Run/xStop_Z0 is active (1).

4

Status_Counter 1

Watchdog status counter 1 (writing is ignored):

0: Watchdog counter 1 has not expired

1: Watchdog counter 1 has expired

Note: This bit can only be read as ‘1’ if Run/xStop_Z1 is active (1).

15-5

Reserved

Not relevant (read=0)

31-16

Key bits

Key bits for writing to this register (read=0).

If bits 31-16=9876h, writing of bits 0-4 of this register has an effect;

otherwise, no effect.

Copyright © Siemens AG 2007. All rights reserved.

46

ERTEC 200 Manual

Technical data subject to change Version 1.1.0