Icu register description, Irq interrupts as fiq interrupt sources, Interrupt control register – Siemens ERTEC200 User Manual

Page 27

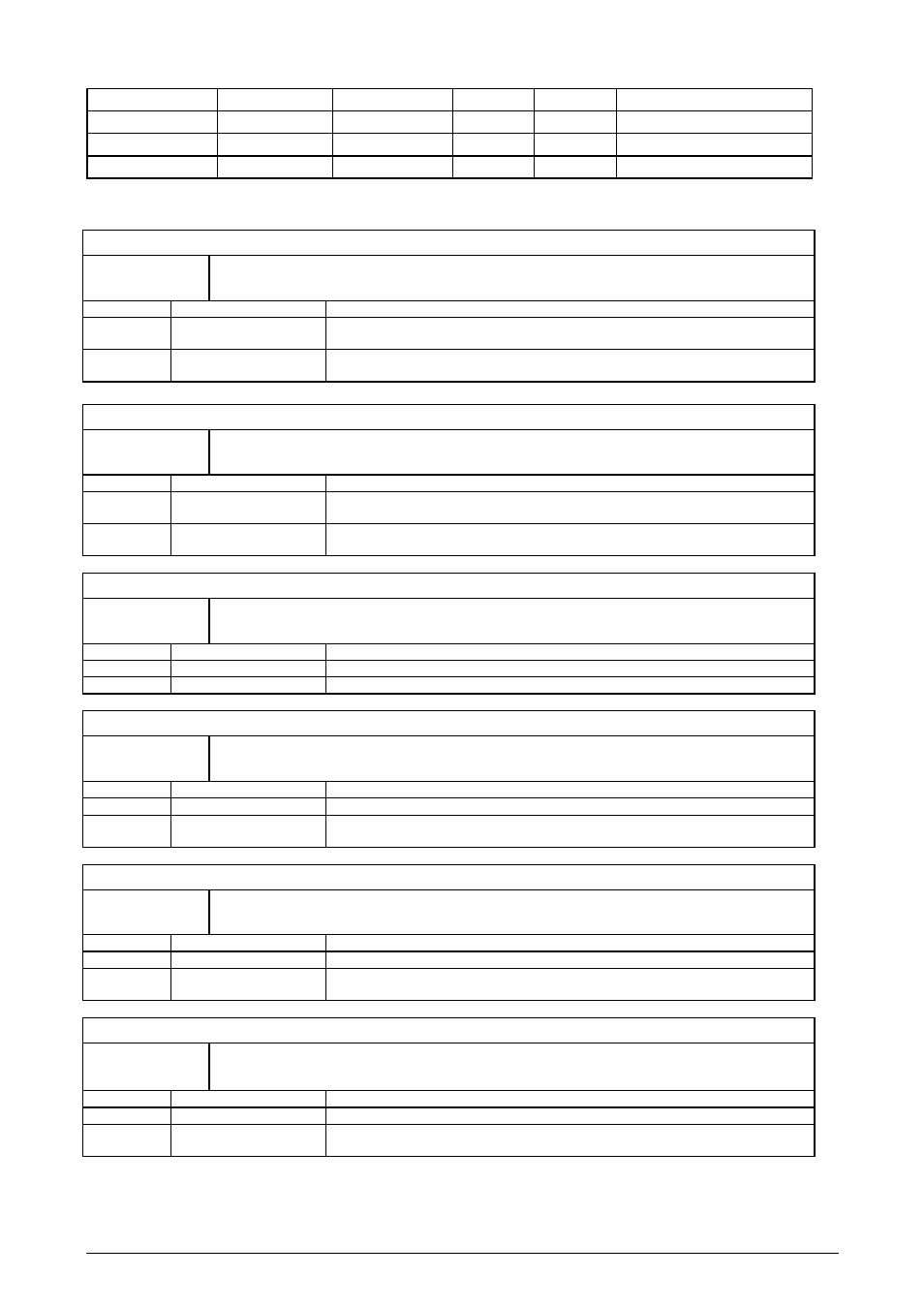

PRIOREG 1

0x0074 4

bytes

R/W

0x0000000F

....

...

...

....

...

...

....

PRIOREG15 0x00AC 4

bytes

R/W

0x0000000F

Priority register 15

Table 4: Overview of Interrupt Control Register

2.9.11 ICU Register Description

IRVEC

R

Addr.: 0x5000_0000 Default:

0xFFFF_FFFF

Description

Interrupt vector register

Input with highest priority pending interrupt request

Bit No.

Name

Description

3:0

IRVEC

For pending, valid interrupt: Binary code of input number.

Default vector: Bit[3:0] = 1

31:4

Vector ID

For pending, valid interrupt: Bit[31:4] = 0.

Default vector: Bit[31:4] = 1

FIVEC

R

Addr.: 0x5000_0004 Default:

0xFFFF_FFFF

Description

Fast interrupt vector register

Number of the highest-priority pending fast interrupt request

Bit No.

Name

Description

2:0

FIVEC

For pending, valid interrupt: Binary code of FIQ number.

Default vector: Bit[2:0] = 1

31:3

Vector ID

For pending valid Bit[31:3] = 0.

Default vector: Bit[31:3] = 1

LOCKREG

R/W

Addr.: 0x5000_0008

Default:

0x0000_0000

Description Priority

lock

register

Specification of a priority for blocking interrupt requests of lower and equal priority

Bit No.

Name

Description

3 – 0

LOCKPRIO

Binary code of lock priority.

7

LOCKENABLE

0=Lock inactive / 1=Lock active

FIQ1SREG

R/W

Addr.: 0x5000_000C

Default: 0x0000_0000

Description

Fast interrupt request 1 select register

Declaration of an IRQ input as FIQ6 (input FIQ6 on FIQ interrupt controller)

Bit No.

Name

Description

3 – 0

FIQ1SREG

Number of the input to be selected (binary code)

7

FIQ1SENABLE

0=Ignore FIQ declaration

0=Take into account FIQ declaration

FIQ2SREG

R/W

Addr.: 0x5000_0010 Default:

0x0000_0000

Description

Fast interrupt request 2 select register

Declaration of an IRQ input as FIQ7 (input FIQ7 on FIQ interrupt controller)

Bit No.

Name

Description

3 – 0

FIQ2SREG

Number of the input to be selected (binary code)

7

FIQ2SENABLE

0=Ignore FIQ declaration

0=Take into account FIQ declaration

IRQACK

R

Addr.: 0x5000_0014 Default:

0xFFFF_FFFF

Description

Interrupt vector register with IRQ acknowledge

Confirmation of highest-priority pending interrupt request by reading

the associated interrupt vector

Bit No.

Name

Description

3 – 0

IRVEC

Binary code of input number

31 - 4

Vector ID

Valid IRQ vector: always ‘0’.

Default vector: always ‘1’ (also bits 3 – 0).

Copyright © Siemens AG 2007. All rights reserved.

27

ERTEC 200 Manual

Technical data subject to change Version 1.1.0