Address assignment of lbu registers, Lbu register description, Table 29: overview of lbu registers – Siemens ERTEC200 User Manual

Page 84: Lbu_p0_rg_h, Lbu_p1_rg_h, Lbu_p2_rg_h, Lbu_p3_rg_h, Lbu_p0_of_l, Lbu_p1_of_l, Lbu_p2_of_l

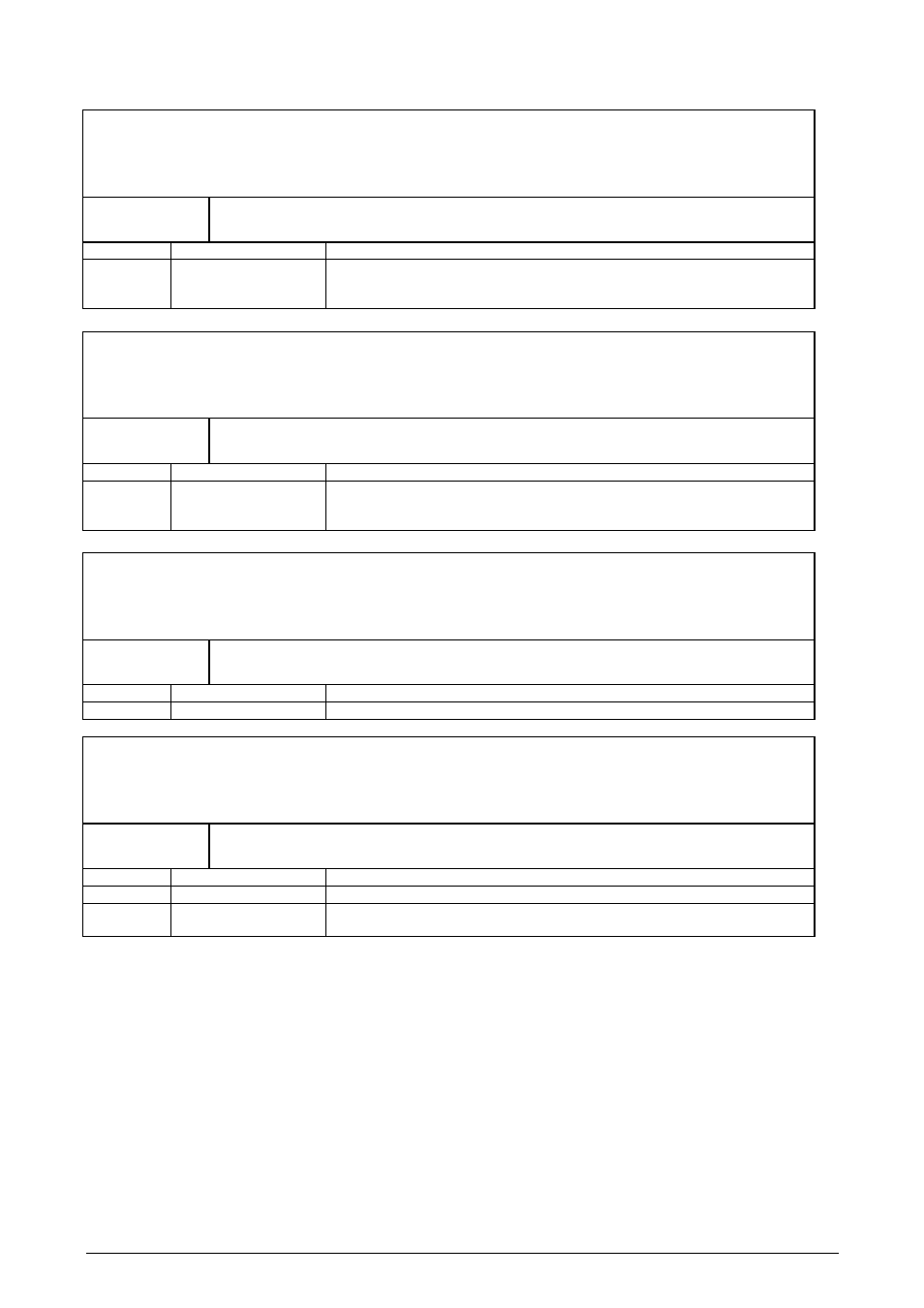

LBU_P0_RG_H

W/R Addr.: LBU_CS_R_N+0x02 Default: 0x0000_0001 (64k)

LBU_P1_RG_H

W/R Addr.: LBU_CS_R_N+0x12 Default: 0x0000_0010 (1M)

LBU_P2_RG_H

W/R Addr.: LBU_CS_R_N+0x22 Default: 0x0000_0020 (2M)

LBU_P3_RG_H

W/R Addr.: LBU_CS_R_N+0x32 Default: 0x0000_0000 (2 k)

Description

High word of LBU Pagex_Range_register

Bit No.

Name

Description

15..0

Upper 16 bits for area setting

15:6 are read-only (value: 000h)

5:0 are read/write accessible

LBU_P0_OF_L

W/R Addr.: LBU_CS_R_N+0x04 Default: 0x0000_0000

LBU_P1_OF_L

W/R Addr.: LBU_CS_R_N+0x14 Default: 0x0000_0000

LBU_P2_OF_L

W/R Addr.: LBU_CS_R_N+0x24 Default: 0x0000_0000

LBU_P3_OF_L

W/R Addr.: LBU_CS_R_N+0x34 Default: 0x0000_2000

Description Low

word

of

LBU Pagex_Offset_register

Bit No.

Name

Description

15..0

Lower 16 bits for offset setting

15:8 are read/write accessible

7:0 are read-only (value: 00h)

LBU_P0_OF_H

W/R Addr.: LBU_CS_R_N+0x06 Default: 0x0000_1010 (KRAM)

LBU_P1_OF_H

W/R Addr.: LBU_CS_R_N+0x16 Default: 0x0000_1000 (IRT-Reg)

LBU_P2_OF_H

W/R Addr.: LBU_CS_R_N+0x26 Default: 0x0000_3000 (EMIF)

LBU_P3_OF_H

W/R Addr.: LBU_CS_R_N+0x36 Default: 0x0000_4000 (Periph.)

Description High

word

of

LBU Pagex_Offset_register

Bit No.

Name

Description

15..0

Upper 16 bits for offset setting

LBU_P0_CFG

W/R Addr.: LBU_CS_R_N+0x08 Default: 0x0000_0000 (16Bit)

LBU_P1_CFG

W/R Addr.: LBU_CS_R_N+0x18 Default: 0x0000_0001 (32Bit)

LBU_P2_CFG

W/R Addr.: LBU_CS_R_N+0x28 Default: 0x0000_0000 (16Bit)

LBU_P3_CFG

W/R Addr.: LBU_CS_R_N+0x38 Default: 0x0000_0001 (32Bit)

Description

Configuration for the individual pages

Bit No.

Name

Description

15..1

Reserved

0

PAGE_X_32

1: Page is a 32-bit page

0: Page is a 16-bit page

Copyright © Siemens AG 2007. All rights reserved.

84

ERTEC 200 Manual

Technical data subject to change Version 1.1.0