Structure of the ertec 200, Figure 1: ertec 200 block diagram, Arm946es – Siemens ERTEC200 User Manual

Page 10: 3 structure of the ertec 200, Page, Port switch, Ertec200, With i-cache, D-cache, D-tcm

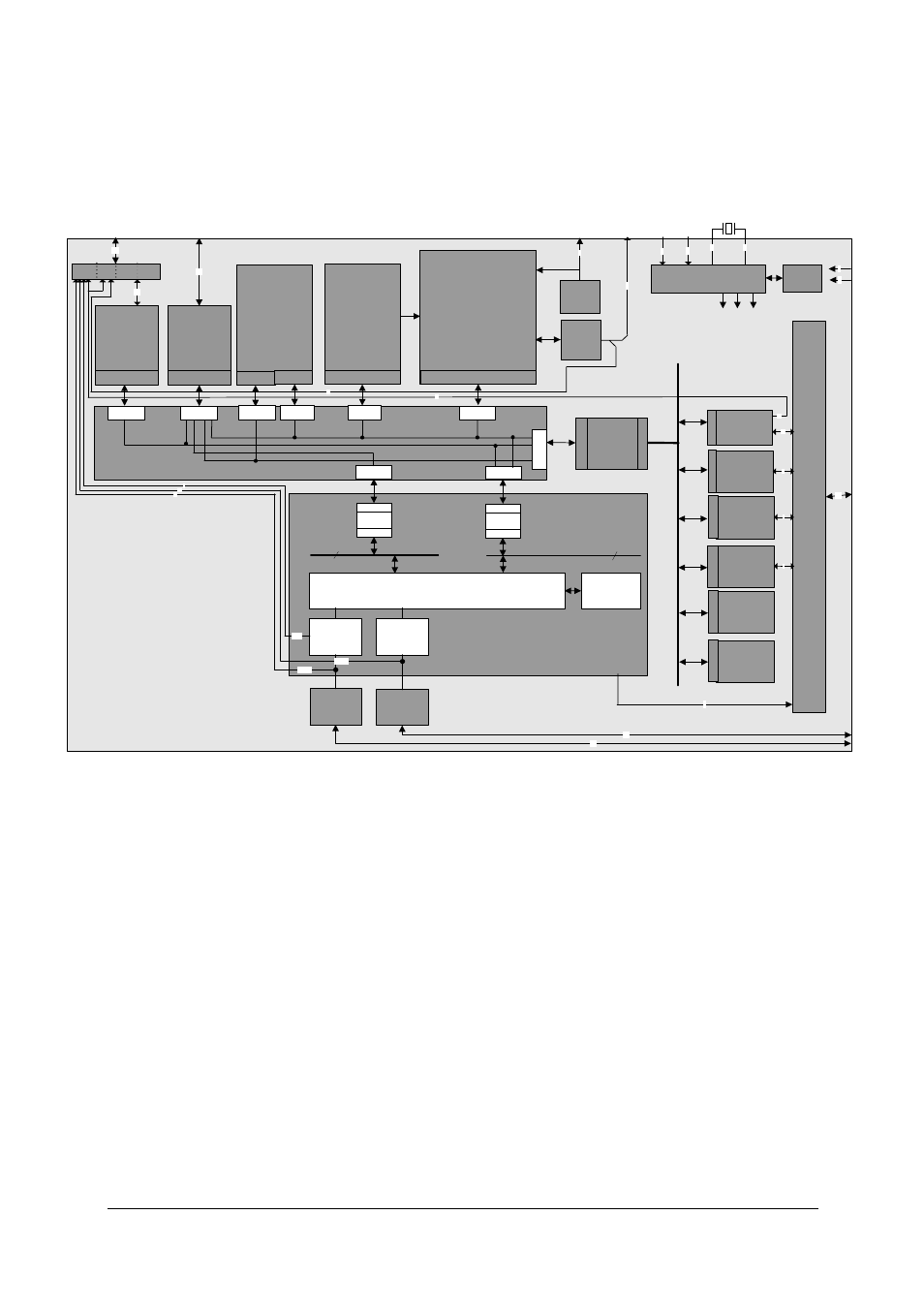

1.3 Structure of the ERTEC 200

The figure below shows the function groups with the common communication paths.

DMA-

Controller

AHB/APB

Bridge

GPIO

Ma

s

te

r

Master

P

P

o

r

t

s

7

APB

50MHz / 32 Bit

74

LBU / MII + SMI /

ETM / GPIO

1 x UART

SPI1

Interface

3 x Timer,

Watchdog,

F-Timer

AR

M

9

cl

o

c

k

50

M

H

z

10

0M

H

z

1

1

25MHz

SC-Bus

(50MHz)

32 Bit

2-Port Switch

Switch Control

K-SRAM

64 kByte

Ethernet-

Port1

Ethernet-

Port2

21

20

32

5

GPIO,

UART,

SPI,

Timer,

Watchdog,

PHY2

AHB-

Wrapper

Slave

Master

Slav

e

Slav

e

2

Slav

e

Boot-

ROM

(8 kByte)

Sl

a

v

e

32

8

1

Test

Multi-Layer-AHB

50 MHz/32Bit

Memory-

Controller

(EMIF)

Slave

Input

stage

MUX/Arb.

MUX/Arb.

MU

X

/A

rb

.

4

Reset

System

Control

Clock-Unit

F_CLK

48

Local

Bus Unit

16 Bit

(LBU)

Master

Input

stage

MUX

ERTEC200

MC-PLL Signals

PHY

(Port 1)

PHY

(Port 2)

ARM946ES

with

I-Cache

(8kByte)

,

D-Cache

(4kByte)

,

D-TCM

(4kByte)

Master

7

BS-

TAP

JTAG / Debug

AHB-

Wrapper

Master

MC-Bus

(50MHz)

32 Bit

Slave

Input

stage

ARM-

Interrupt-

Controller

Slave

Decode

Input

stage

Slave

Decode

1

MII-0

MII-1

PLL

48

SMI

3

16

16

External

Memory Interface

PHY1

1

REF_

CLK

ETM

Interface

TRACE_

CLK

14

1

13

13

Sl

a

v

e

Sl

a

v

e

Sla

v

e

Figure 1: ERTEC 200 Block Diagram

Copyright © Siemens AG 2007. All rights reserved.

Page

10

ERTEC 200 Manual

Technical data subject to change Version 1.1.0