Lbu address mapping, Table 21: setting of various offset areas, Host etec200 lbu – Siemens ERTEC200 User Manual

Page 77

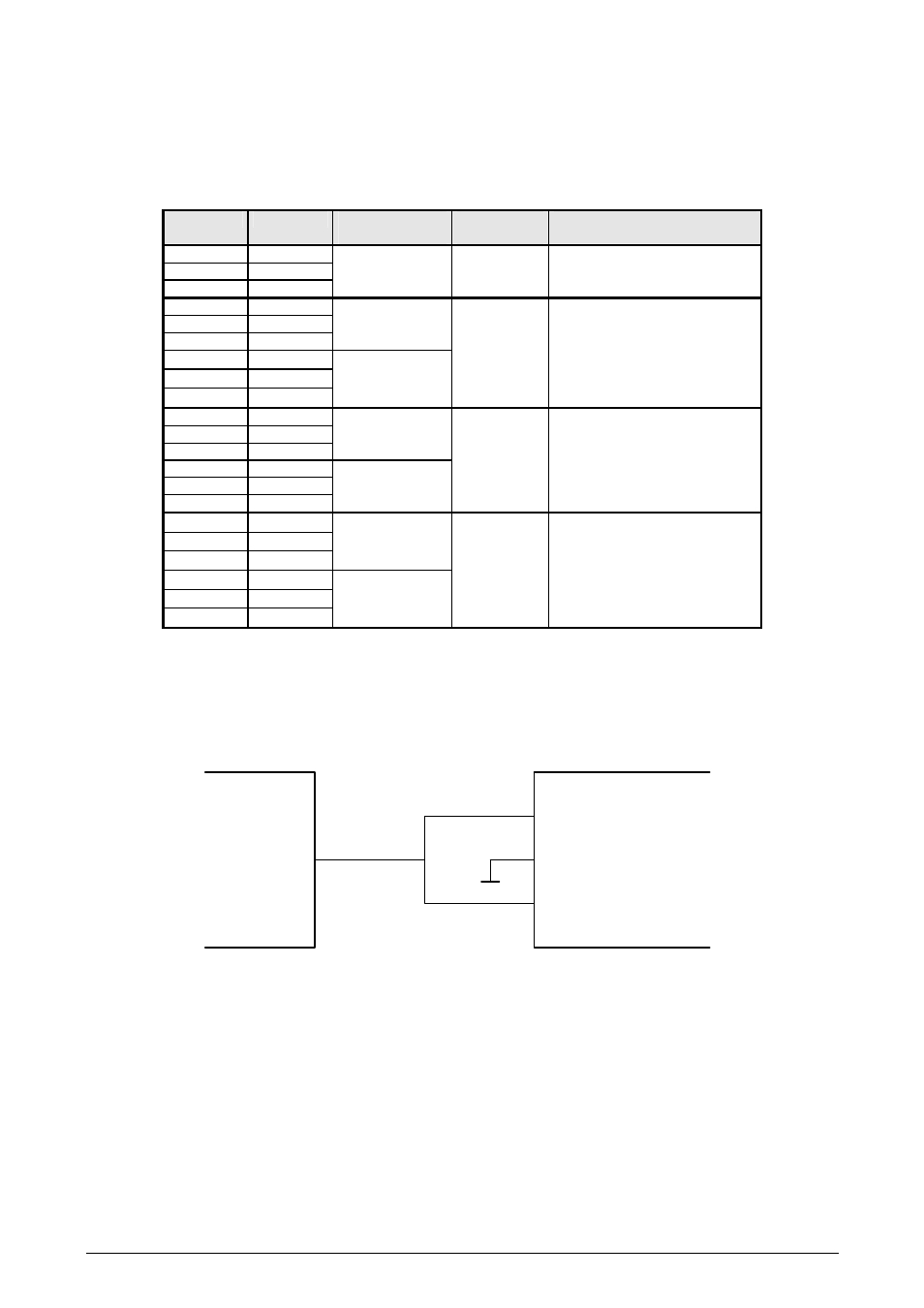

7.3 LBU Address Mapping

The following table illustrates an example of the ERTEC 200 Address Mapping from the Perspective of an External Host

Processor:

Seg(1:0)

AD(19:0)

SEGMENT

Distribution

SEGMENT

Size

Comment

00 0_0000h 1MB

1MB

Page SDRAM (1 Mbyte)

00

Range: 0010 0000h

00 F_FFFFh

Offset: 2000 0000h

01 0_0000h

64k

1MB

Page KRAM (64 Kbytes)

01

Range: 0001 0000h

01 0_FFFFh

Offset: 1010 0000h

01 1_0000h 64k

01 Mirrored

01 F_FFFFh

10 0_0000h 128k

1MB

Page ext. SRAM (128 Kbytes)

10

Range: 0002 0000h

10 1_FFFFh

Offset: 3000 0000h

10 2_0000h 128k

10 Mirrored

10 F_FFFFh

11 0_0000h 16k

1MB

Page APB I/O

11

Range: 0000 4000h

11 0_3FFFh

Offset: 4000 0000h

11 0_4000h 16k

11 Mirrored

11 F_FFFFh

Table 22: Address Mapping from the Perspective of an External Host Processor on the LBU

Port

In this example, a maximum of 1 MB is addressed. The addresses A[19:0] of the host processor are wired to the

LBU_ADR [19:0] for this purpose. In addition, the addresses A[21:20] are necessary for the segment selection. These

are connected to the LBU pins LBU_SEG[1:0].

Host

ETEC200

LBU

ADR(21:0)

ADR(19:0)

ADR(21:20)

LBU_ADR(19:0)

LBU_ADR(20)

LBU_SEG(1:0)

Figure 12: Interconnection of Addresses between Host and ERTEC 200 LBU

Copyright © Siemens AG 2007. All rights reserved.

77

ERTEC 200 Manual

Technical data subject to change Version 1.1.0