Spi register description, Address assignment of spi register, Table 15: overview of spi registers – Siemens ERTEC200 User Manual

Page 56: Sspcr0, Sspcr1

4.7.2

SPI Register Description

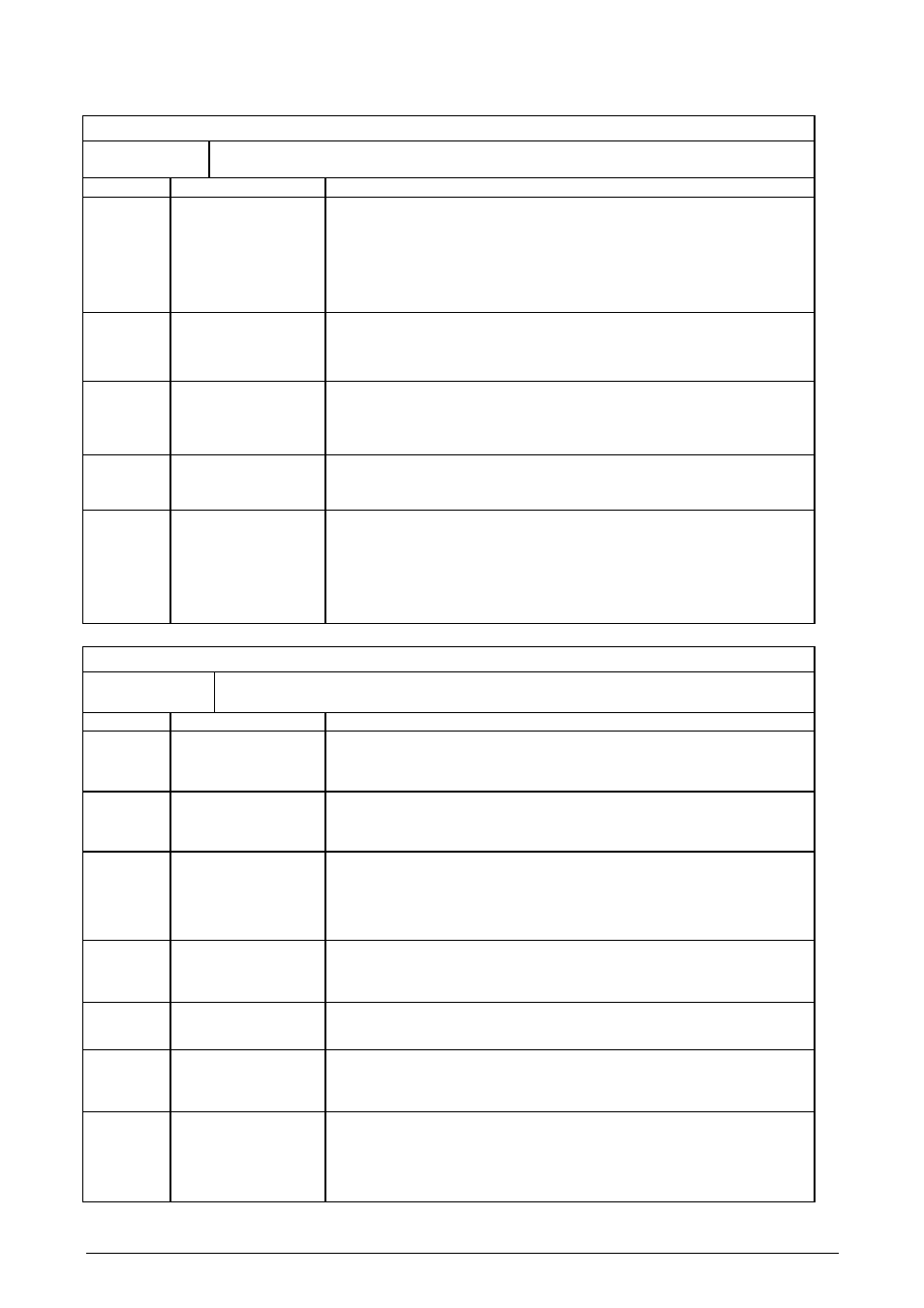

SSPCR0

R/W Addr.: 0x4000_2200 Default: 0x0000

Description

Control register 0. Configuration frame format and baud rate for SPI.

Bit No.

Name

Description

3 - 0

DSS

Data Size Select

0000 Reserved (undefined) 1000 9-Bit Data

0001 Reserved (undefined) 1001 10-Bit Data

0010 Reserved (undefined) 1010 11-Bit Data

0011 4-Bit Data 1011 12-Bit Data

0100 5-Bit Data 1100 13-Bit Data

0101 6-Bit Data 1101 14-Bit Data

0110 7-Bit Data 1110 15-Bit Data

0111 8-Bit Data 1111 16-Bit Data

5 - 4

FRF

Frame Format

00

Motorola SPI frame format

01

TI synchronous serial frame format

02

National Microwire frame format

03

Reserved (undefined operation)

6 SPO

Serial Clock Output

Polarity

Can only be used in Motorola SPI frame format.

0 Received bits are engaged on the rising edge of SCLKIN/OUT.

Sent bits are switched on the falling edge of SCLKIN/OUT.

1 Received bits are engaged on the falling edge of SCLKIN/OUT.

Sent bits are switched on the rising edge of SCLKIN/OUT.

7 SPH

Phase of

Transmission Bit

Can only be used in Motorola SPI frame format.

0 Received MSB is expected after frame signal has gone to Low

1 Received MSB is expected ½ clock cycle after frame signal has gone to Low

15-8 SCR

Serial Clock Rate

The serial clock rate is taken for calculation of the Transmit/Receive bit rate.

The calculation formula is as follows:

F

SSPCLK

----------------------------------------

CPSDVSR x (1 + SCR)

SCR := 1 to 255

CPSDVSR := 2 to 254 (for a description, refer to SSPCPSR Register)

SSPCR1

R/W Addr.: 0x4000_2204 Default: 0x0000

Description

Control register 1. Configuration frame format and baud rate for SPI.

Bit No.

Name

Description

0 RIE

Receive FIFO interrupt enable:

0 = Receive FIFO half full or more interrupt SSPRXINTR is disabled

1 = Receive FIFO half full or more interrupt SSPRXINTR is enabled

1 TIE

Transmit FIFO interrupt enable:

0 = Transmit FIFO half full or less interrupt SSPTXINTR is disabled

1 = Transmit FIFO half full or less interrupt SSPTXINTR is enabled

2 RORIE

Receive FIFO overrun interrupt enable:

0 = FIFO overrun display interrupt SSPRORINTR is disabled

(When this bit is deleted, the SSPRORINTR interrupt is also deleted if this interrupt

was currently being enabled)

1 = FIFO overrun display interrupt SSPRORINTR is enabled

3

LBM

Loop back mode

0 = Normal serial operation is active

1 = Loop back mode is active. (The output of the Transmit serial shifter is connected

internally to the input of the Receive serial shifter.)

4 SSE

Synchronous

serial port enable:

0 = SPI port is disabled

1 = SPI port is enabled

5 MS

Master/slave

mode

select

(This bit can only be changed if Bit 4 SSE = 0)

0 = Device is master (default)

1 = Device is slave

6 SOD

Slave-Mode-Output

Disable

(This bit is only relevant in slave mode MS = 1)

In “Multiple slave systems," the master can send a broadcast message to all slaves in

the system in order to ensure that only one slave drives data at its Transmit output

0 = SPI can drive the SSPTXD output in slave mode

1 = SPI must not drive the SSPTXD output in slave mode

Copyright © Siemens AG 2007. All rights reserved.

56

ERTEC 200 Manual

Technical data subject to change Version 1.1.0