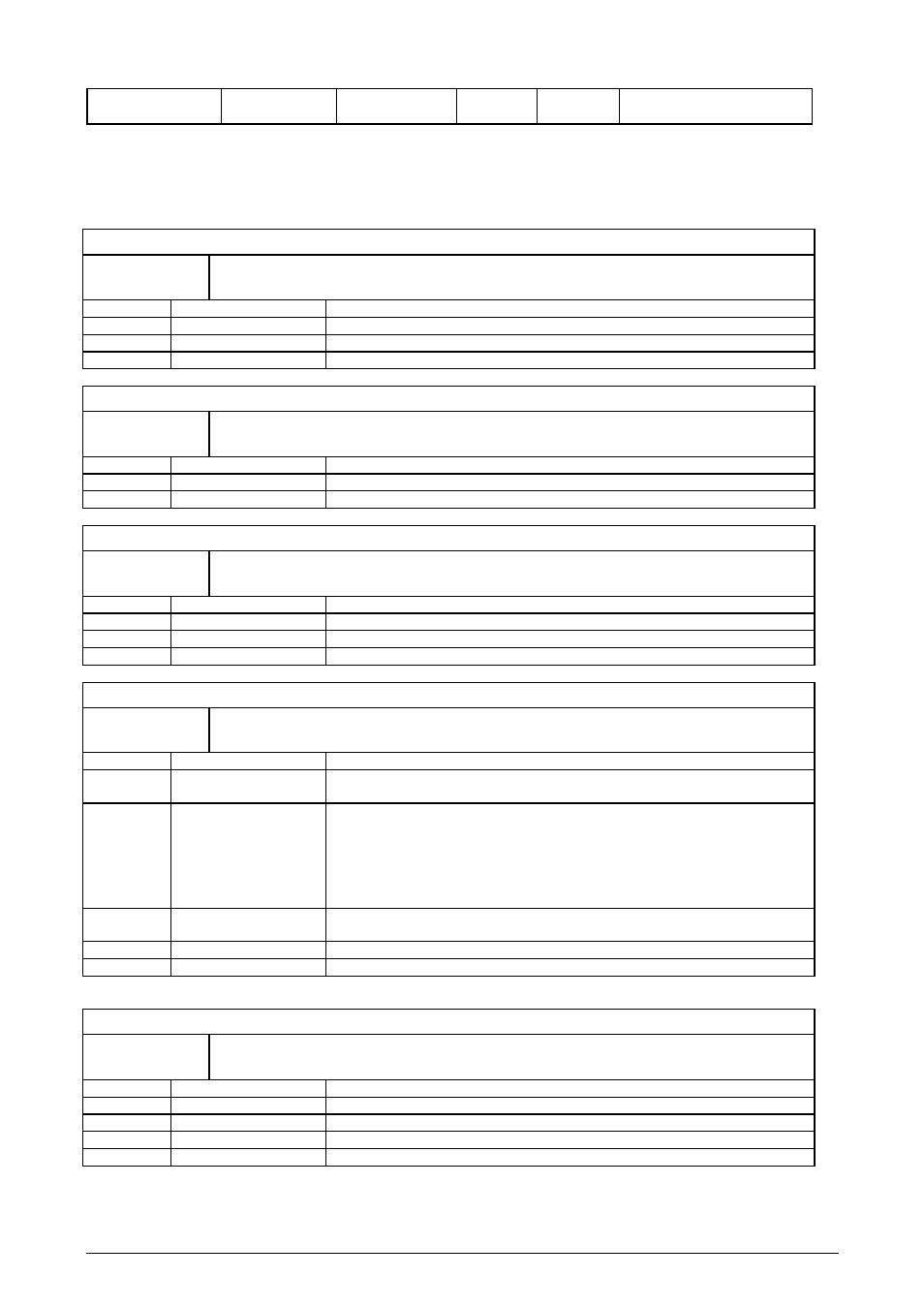

System control register description, System control register, Address assignment of system control registers – Siemens ERTEC200 User Manual

Page 59: Id_reg, Boot_reg, Config_reg, Res_ctrl_reg, Res_ stat _reg

UART_CLK 0x0070 4

bytes R/W

0x00000000

UART clock selection

50MHz/6MHz

Table 16: Overview of System Control Registers

4.8.2

System Control Register Description

ID_REG

R

Addr.: 0x4000_2600

Default: 0x4027_0100

Description

Identification of ERTEC 200.

Bit No.

Name

Description

31..16

ERTEC200-ID

ERTEC 200 identifier: 4027h

15..8

HW-RELEASE

HW release: 01h

7..0

METALL-FIX

Metal fix: 00h

BOOT_REG

R

Addr.: 0x4000_2604 Default: Bootpins[3:0]

Description

Boot mode pins BOOT[3:0] can be read

Bit No.

Name

Description

31..4 Reserved

Reserved

3 .. 0

BOOT[3:0]

Reading of Boot[3] pin

CONFIG_REG

R Addr.:

0x4000_2608

Default:Configpins[6:1]

Description

ERTEC 200 config pins CONFIG[6:1] can be read.

Bit No.

Name

Description

31..7 Reserved

Reserved

6 .. 1

CONFIG[6:1]

Reading of CONFIG[6:1] pin

0 Reserved

Reserved

RES_CTRL_REG

W/R

Addr.: 0x4000_260C

Default: 0x0000_0004

Description

Control register for reset of ERTEC 200

Bit No.

Name

Description

31..13 Reserved

Reserved

12:3

PULSE_DUR

Pulse duration of SW or watchdog reset.

T

RES_PULSE

= (8 x n + 8) x T

CLK

;

T

CLK

:

APB clock period (1/50 MHz = 20 ns)

n:

Value of PULSE_DUR (0 .. 1023)

The integrated PHYs require a reset duration of > 100

µs. This requires the

setting n > 625.

2 EN_WD_SOFT_

RES_IRTE

0: The IRTE switch controller is not reset for the watchdog/soft reset.

1: The IRTE switch controller is reset for the watchdog/soft reset.

1

XRES_SOFT

1: Software reset (not latching)

0

WD_RES_FREI

1: Enable watchdog reset

RES_ STAT _REG

R Addr.:

0x4000_2610

Default: 0x0000_0004

Description

Status register for reset of ERTEC 200.

Only the bit of the last reset event occurrence is set. The two other bits are reset.

Bit No.

Name

Description

31..3 Reserved

Reserved

2

HW_RESET

1: Last reset was PowerOn or Hardware reset

1

SW_RESET

1: Last reset was Software reset

0

WD_RESET

1: Last reset was Watchdog reset

Copyright © Siemens AG 2007. All rights reserved.

59

ERTEC 200 Manual

Technical data subject to change Version 1.1.0