I/o on apb bus, Boot rom, Bus system of the ertec 200 – Siemens ERTEC200 User Manual

Page 33: Multilayer ahb” communication bus, Ahb arbiter, Ahb master-slave coupling, Apb i/o bus, Table 6: overview of ahb master-slave access, 4i/o on apb bus

4

I/O on APB bus

The ERTEC 200 block has multiple I/O function blocks. They are connected to the 32-bit APB I/O bus. The ARM946E-S,

DMA controller and LBU interface can access the I/O. The following I/O are available.

8 Kbyte Boot ROM

32-bit GPIO (*)

UART

SPI

interface

Timer 0 - 2

F-timer

Watchdog

System control register

(*) The complete 32 bits for GPIO input/output are only available if alternative functions are not assigned.

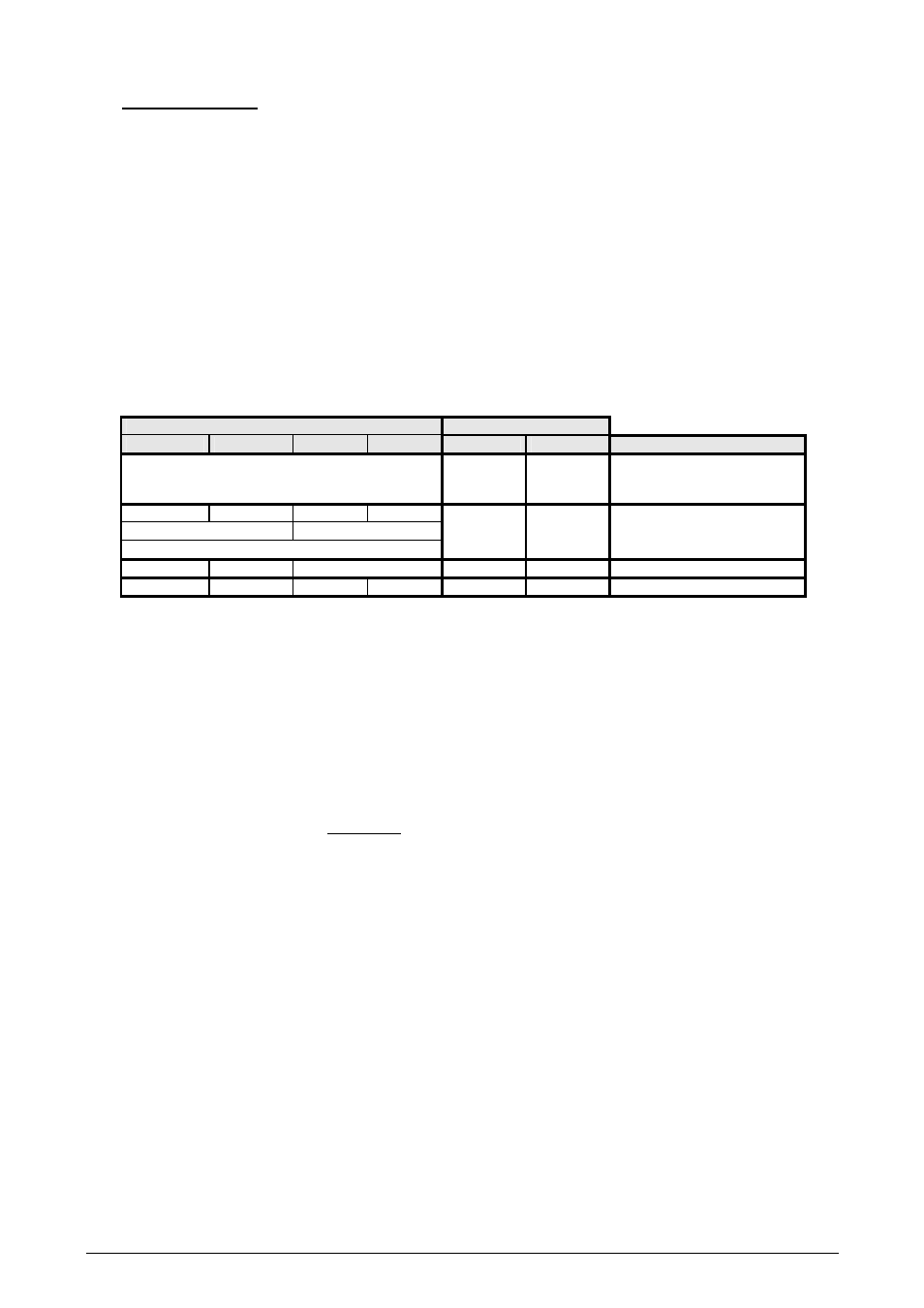

The I/O function blocks connected to the APB bus have data interfaces of different widths. The data width and the

supported access mechanisms are shown in the table below. Non-permitted access types such as byte-by-byte loading

of timer reload registers are not intercepted on the hardware side.

Access Types

Wait States on the AHB

Bit 31:24

Bit 23:16

Bit 15:8

Bit 7:0

Read

Write

Function Block

32 bit

2

0

Timer0/1/2, F-Counter,

System-Control-Register,

Watchdog, Boot_Rom

8 bit

8 bit

8 bit

8 bit

16 bit

16 bit

32 bit

2 0

GPIO

- -

16

bit

2 0

SPI1

- -

-

8

bit

2 0

UART

Table 7: Access Type and Data Width of the I/O

Accesses to non-decoded-out memory or register areas trigger an FIQ1 interrupt. Access by a generated “Ready” signal

from the APB address decoder is closed. Write accesses do not affect the system. Read accesses supply undefined

data.

4.1 BOOT

ROM

The ERTEC 200 is implemented with a BOOT ROM whose integrated opcode enables software to be downloaded from

an external storage medium. Various routines are available for the different boot and download modes. In order to select

the source and the mode, four BOOT[3:0] inputs are available on the ERTEC 200. During the active reset phase, the

boot pins are read in and stored in the BOOT REG register in the system control register area.

After startup of the processor, the system branches to the appropriate BOOT routine based on the coding and the

download is performed. After the download is complete, the loaded functions are executed.

After RESET has become inactive, the BOOT pins are available as normal EMIF pins.

The following actions lead to a boot operation:

• HW

reset

• Watchdog

Reset

•

Software reset caused by setting the XRES_SOFT bit in the reset control register (system control register area)

Copyright © Siemens AG 2007. All rights reserved.

33

ERTEC 200 Manual

Technical data subject to change Version 1.1.0