Qvz_ahb_m, Qvz_apb_adr, Qvz_emif_adr – Siemens ERTEC200 User Manual

Page 61: Mem_swap, M_lock_ctrl

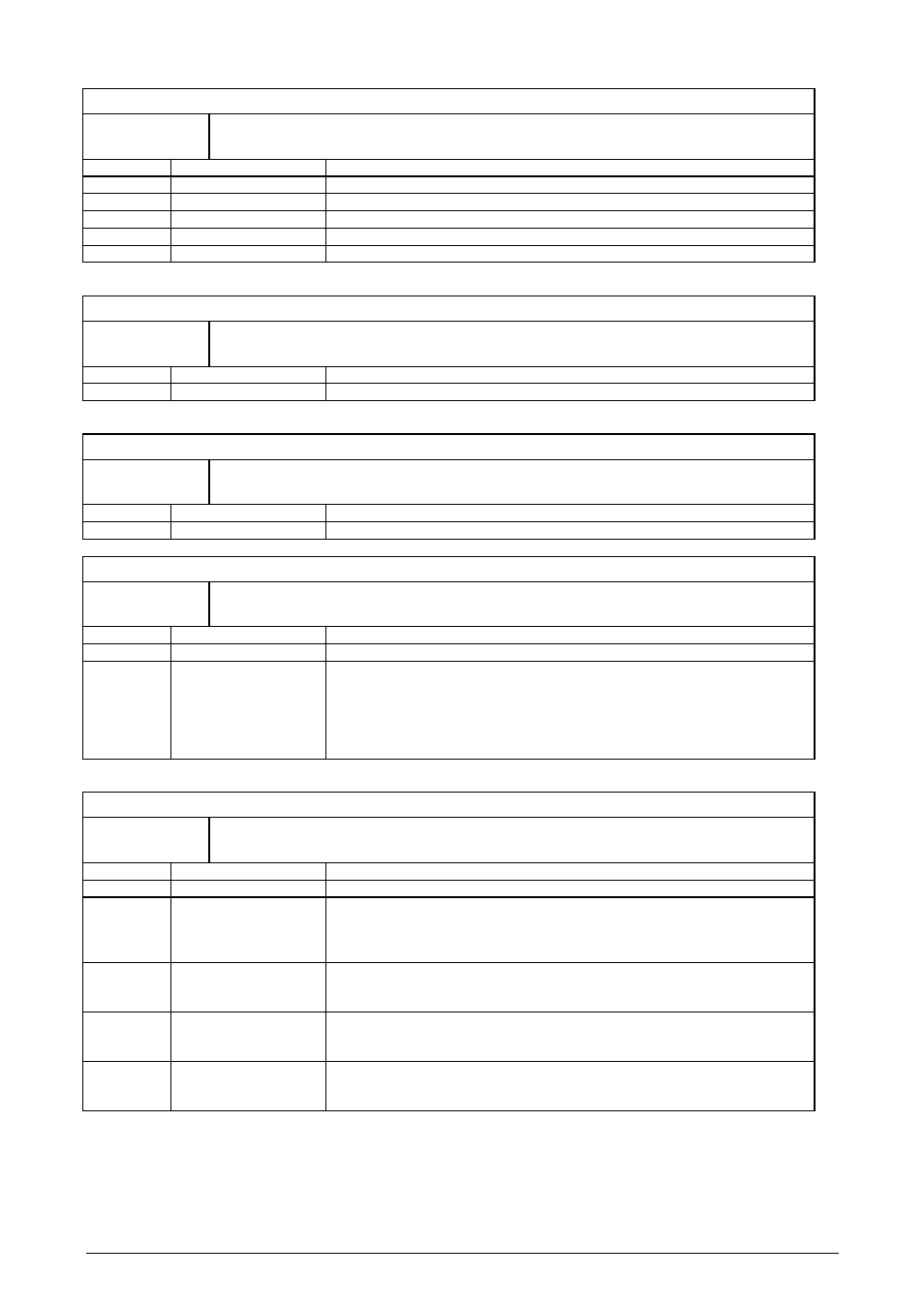

QVZ_AHB_M

R Addr.:

0x4000_2630

Default: 0x0000_0000

Description

Master identifier of an incorrect addressing on the multilayer AHB

Bit No.

Name

Description

31:4 Reserved

Reserved

3 QVZ_AHB_DMA

DMA

2 QVZ_AHB_IRT

IRT

1 QVZ_AHB_LBU

LBU

0 QVZ_AHB_ARM946

ARM946

QVZ_APB_ADR

R Addr.:

0x4000_2634

Default: 0x0000_0000

Description

Address of incorrect addressing on AHB

Bit No.

Name

Description

31:0 QVZ_APB_ADR

Address

QVZ_EMIF_ADR

R Addr.:

0x4000_2638

Default: 0x0000_0000

Description

Address that leads to timeout on EMIF

Bit No.

Name

Description

31:0 QVZ_EMIF_ADR

Address

MEM_SWAP

R/W

Addr.: 0x4000_2644

Default: 0x0000_0000

Description

Memory Swapping in Segment 0 on the AHB (ROM, EMIF-SDRAM, EMIF-Standard-Memory)

Bit No.

Name

Description

31:2 Reserved

Reserved

1:0

MEM_SWAP

Selection of memory in Segment 0 on the AHB:

00: Boot ROM starting with Addr 0h

01: EMIF-SDRAM starting at Adr 0h

10: EMIF-Standard-Memory starting at Adr 0h

11: No memory starting from Addr 0h, Locked I-Cache can be placed on

Addr 0h

M_LOCK_CTRL

R/W

Addr.: 0x4000_264C

Default: 0x0000_0000

Description

AHB master lock enable. Master-selective enable of AHB lock functionality.

Bit No.

Name

Description

31:4 Reserved

Reserved

3

Reserved

Select arbitration algorithm for AHB arbiter (ARB_MODE).

0: Round robin

1: Fixed priority assignment

This bit should not be changed (default: round robin)!

2

Reserved

Lock enable of AHB master IRT:

0: Lock disabled

1: Lock enabled

1

Reserved

Lock-Enable AHB-Master LBU:

0: Lock disabled

1: Lock enabled

0

Reserved

Lock enable of AHB master ARM9:

0: Lock disabled

1: Lock enabled

Copyright © Siemens AG 2007. All rights reserved.

61

ERTEC 200 Manual

Technical data subject to change Version 1.1.0