Uart interface – Siemens ERTEC200 User Manual

Page 48

4.6 UART

Interface

A UART interface is implemented in the ERTEC 200. The inputs and outputs of the UART interface are available as an

alternative function at GPIO port [12:8]. For this purpose, the I/O must be assigned to the relevant inputs and outputs and

the alternative function must be assigned (see GPIO register description). If the UART is used, the pins are no longer

available as standard I/O. The data bit width for read/write access on the APB bus is 8 bits.

The following signal pins are available for the UART on the ERTEC 200.

•

Transmit cable

1

TXD

• Receive

cable

1

RXD

•

Control cable

3

DCD_N

CTS_N

DSR_N

The UART is implemented as ARM Prime Cell

TM

(PL010) macros. It is similar to standard UART 16C550. For a detailed

description, refer to /5/.

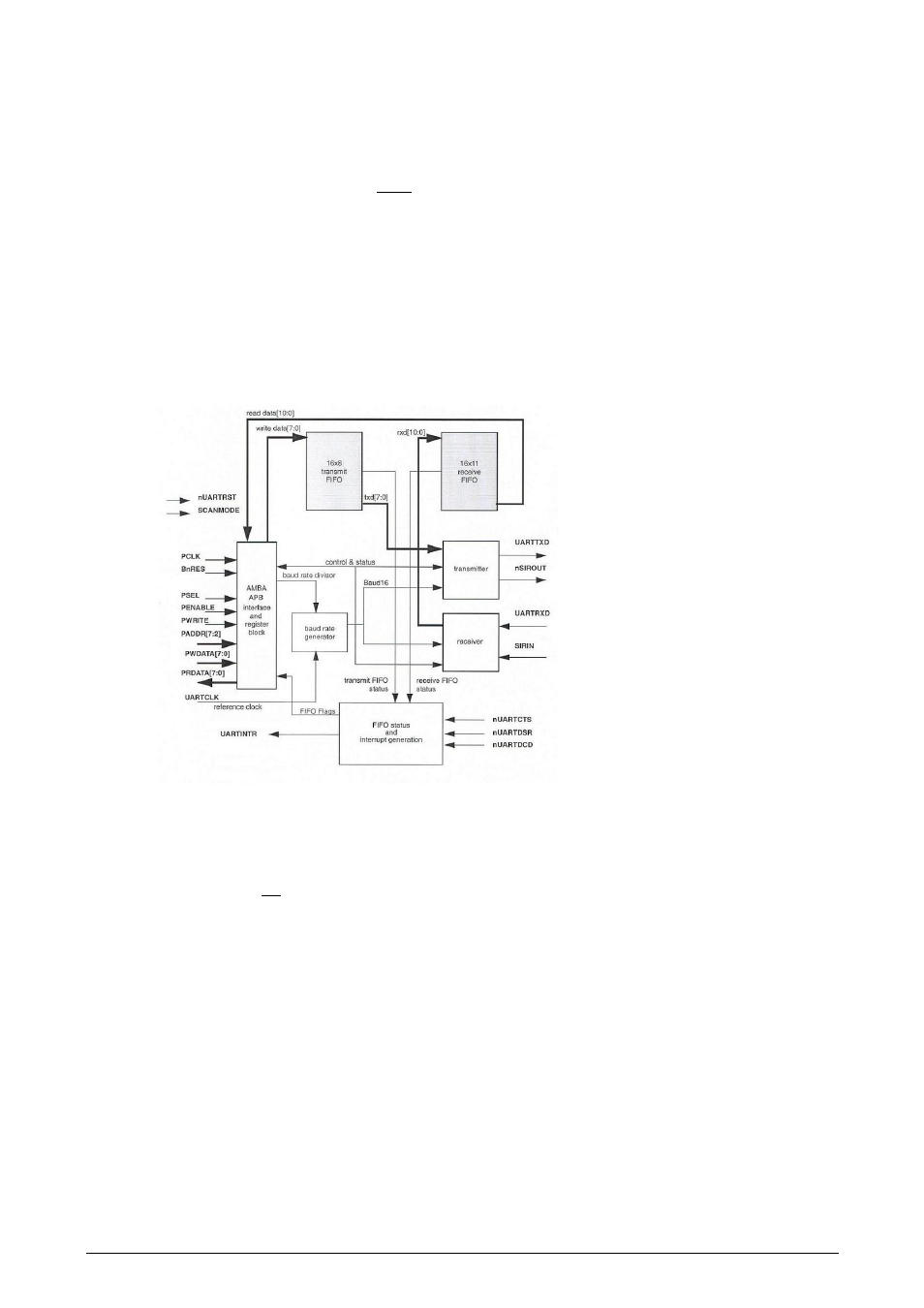

The figure below shows the structure of the UART.

Figure 7: Block Diagram of UART

The UARTs differ from standard UART 16C550 as follows:

•

Receive FIFO trigger level is set permanently to 8 bytes.

•

Receive errors are stored in the FIFO.

• Receive

errors

do

not generate an interrupt.

•

The internal register address mapping and the register bit functions are different.

The following standard UART 16C550 features are not supported:

•

1.5 Stop bits

•

“Forcing stick parity” function

The UART has an interrupt source:

•

UARTINTR

UART – group interrupt

The interrupt is available on the IRQ interrupt controller of the ARM946E-S.

The UART can be controlled by the AEM946 processor or the DMA controller. In DMA mode, the FIFO must be switched

off because FIFO does not indicate the fill level. Because the DMA controller is only a single-channel controller, only

send or receive control can take place via the DMA controller. The other channel must be controlled via software.

Copyright © Siemens AG 2007. All rights reserved.

48

ERTEC 200 Manual

Technical data subject to change Version 1.1.0