Extended config – Siemens ERTEC200 User Manual

Page 73

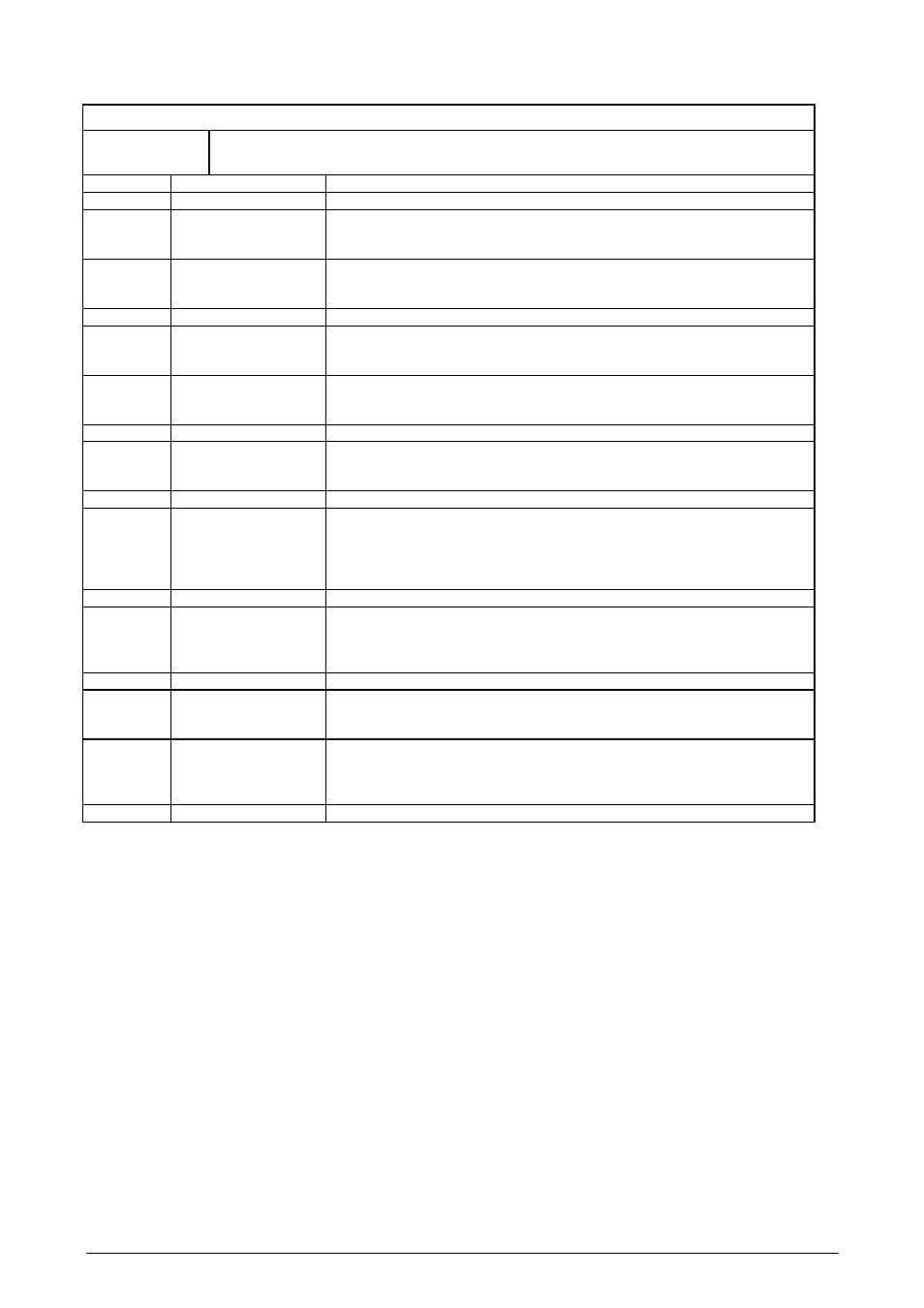

Extended Config

W/R Addr.: 0x7000_0020 Default: 0x0303_0000

Description

Setting of additional functionalities

Bit No.

Name

Description

31 Reserved

Reserved

30

TEST_1

Test Mode 1

0: 200 µs delay after system reset (SDRAM power-up)

1: Delay after system reset is immediately terminated

29

TEST_2

Test Mode 2

0: Normal function

1: All SDRAM accesses are misses

28..26 Reserved

Reserved

25

ADB

Active data bus

After each access to the SDRAM, the data bus is driven actively to 1 in order

to support integrated pull-ups.

24

ASDB

Asynchronous active data bus

After each access to the asynchronous area, the data bus is driven actively

to 1 at the end of the Hold phase in order to support integrated pull-ups.

23..20 Reserved

Reserved

19

TEST_3

Test Mode 3

0: Normal function

1: DTR_N = Test Output

18 Reserved

Reserved

17..16

BURST_LENGTH

SDRAM burst length

00: 1

01: 2

10: Full Page, Read INCR_S burst length = 4

11: Full Page, Read INCR_S burst length = 8

15 Reserved

Reserved

14

TRCD/TCD

Time between the SDRAM commands

Activate and read/write, precharge and activate

0: 1 AHB clock cycles

1: 2 AHB clock cycle

13..9 Reserved

Reserved

8

SDSIZE

SDRAM bank size

0: 32-bit data bus

1: 16-bit data bus

7

ATIRQ

0: Timeout watchdog for asynchronous accesses disabled

1: Timeout watchdog for asynchronous accesses enabled

After the watchdog expires (256 AHB clock cycles), an interrupt is triggered.

Setting Bit 7 to 0 deletes interrupt source.

6..0 Reserved

Reserved

Programming specification for EMIR registers:

For a correct setting of the SDRAM, the values for Burst_Length and SDRAM bank width must match up in the Extended

Config register. The bits must be set before the MODE-Register-SET command is initiated; otherwise, they are not

transferred to the SDRAM. The Mode-Register-Set command is initiated by writing to the bits [15:8] of the SDRAM-

Bank-Config register when bit 29 = 1 in the SDRAM Refresh Control register.

SDRAM 32-bit data width: Extended Config[8] = 0

Extended Config[17:16] = 11 Full Page, Read INCR_S Burst Length = 8

Extended Config[17:16] = 10 Full Page, Read INCR_S Burst Length = 4

Extended Config[17:16] = 00 Burst Length = 1

SDRAM 16-bit data width: Extended Config[8] = 1

Extended Config[17:16] = 11 Full Page, Read INCR_S Burst Length = 8

Extended Config[17:16] = 10 Full Page, Read INCR_S Burst Length = 4

Extended Config[17:16] = 01 Burst Length = 2

All other settings cause malfunctions

The Mode Register Set command is initiated by writing to the bit in the register SDRAM_Bank_Config[15:8]. (Register

SDRAM_Refresh-Control[29] =1)

Copyright © Siemens AG 2007. All rights reserved.

73

ERTEC 200 Manual

Technical data subject to change Version 1.1.0