Spi register description – Siemens ERTEC200 User Manual

Page 57

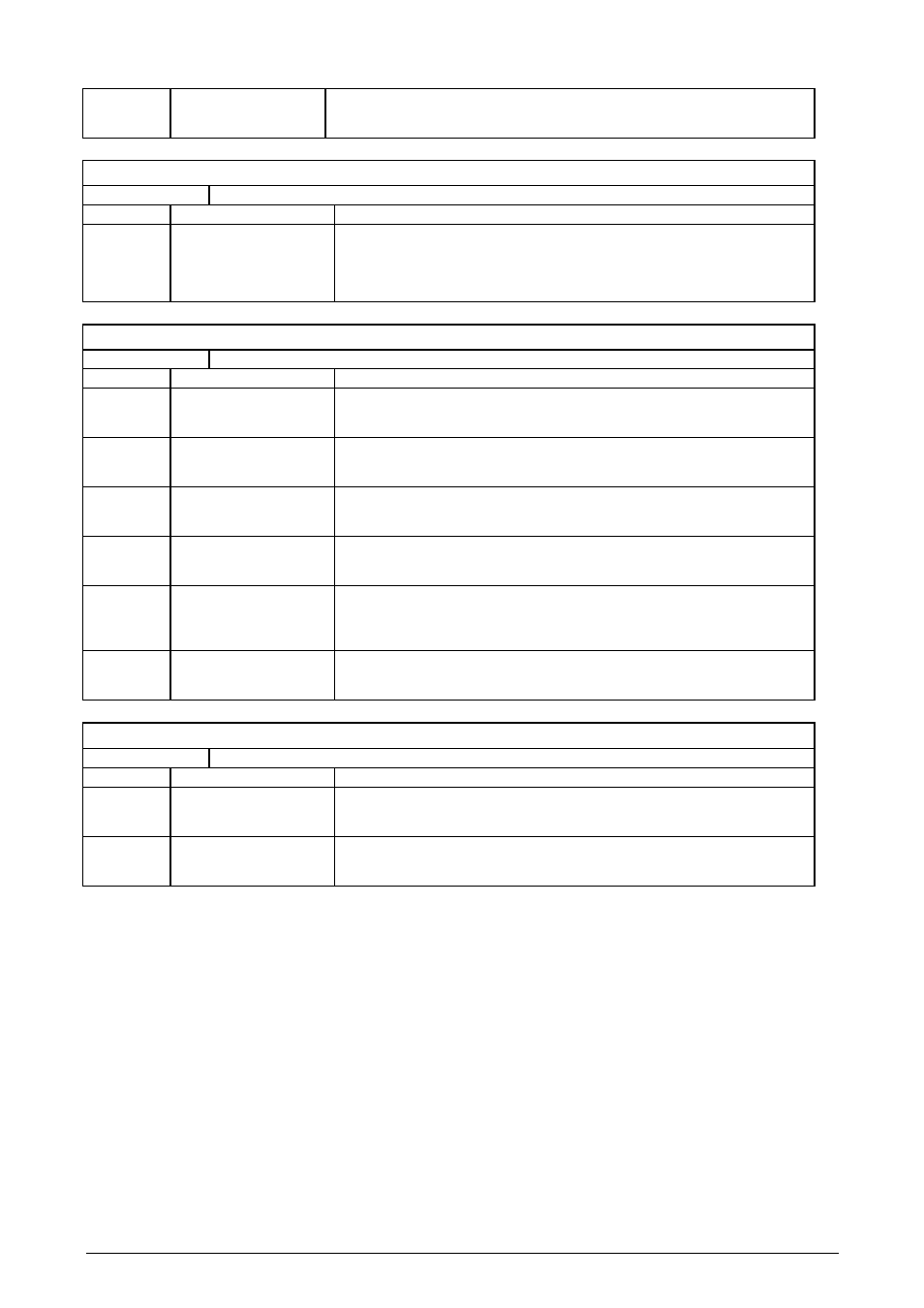

15-7 -------

Reserved

Read: Value is undefined

Write: Should always be written with zero

SSPDR

R/W Addr.: 0x4000_2208 Default: 0x----

Description

SPI data register

Bit No.

Name

Description

15-0 DATA

(15:0)

Transmit/Receive FIFO

Read = Receive FIFO

Write = Transmit FIFO

(If < 16 bits of data, the user must write the data to the Transmit FIFO in the proper

format. When data are read, they are read out correctly from the Receive FIFO.)

SSPSR

R

Addr.: 0x4000_220C Default: 0x0000

Description

SPI status register

Bit No.

Name

Description

0 TFE

Transmit FIFO empty

0 = Transmit FIFO is not empty

1 = Transmit FIFO is empty

1 TNF

Transmit FIFO not full

0 = Transmit FIFO is full

1 = Transmit FIFO is not full

2 RNE

Receive FIFO not empty

0 = Receive FIFO is empty

1 = Receive FIFO is not empty

3 RFF

Receive FIFO full

0 = Receive FIFO is not full

1 = Receive FIFO is full

4 BSY

SPI busy flag

0 = SPI is

1 = SPI is sending and/or receiving a frame or the Transmit FIFO is not

empty.

15-5 ------------

Reserved

Read: Value is undefined

Write: Should always be written with zero

SSPCPSR

R/W Addr.: 0x4000_2210 Default: 0x0000

Description

SPI clock prescale register

Bit No.

Name

Description

7 - 0

CPSDVSR

Clock prescale divisor

(Value between 2 and 254. For formula, refer to SSPCR0 Register.)

When the value is read, bit 0 is always zero.

15-5 ------------

Reserved

Read: Value is undefined

Write: Should always be written with zero

Copyright © Siemens AG 2007. All rights reserved.

57

ERTEC 200 Manual

Technical data subject to change Version 1.1.0