Dma register address assignment, Description of dma registers, Dma-controller – Siemens ERTEC200 User Manual

Page 86: Table 30: dma transfer modes, Table 31: i/o synchronization signals, Dmac0srcaddrreg) dma-source address, Dmac0destaddrreg) dma-destination address, Dmac0contrreg) channel control (*)

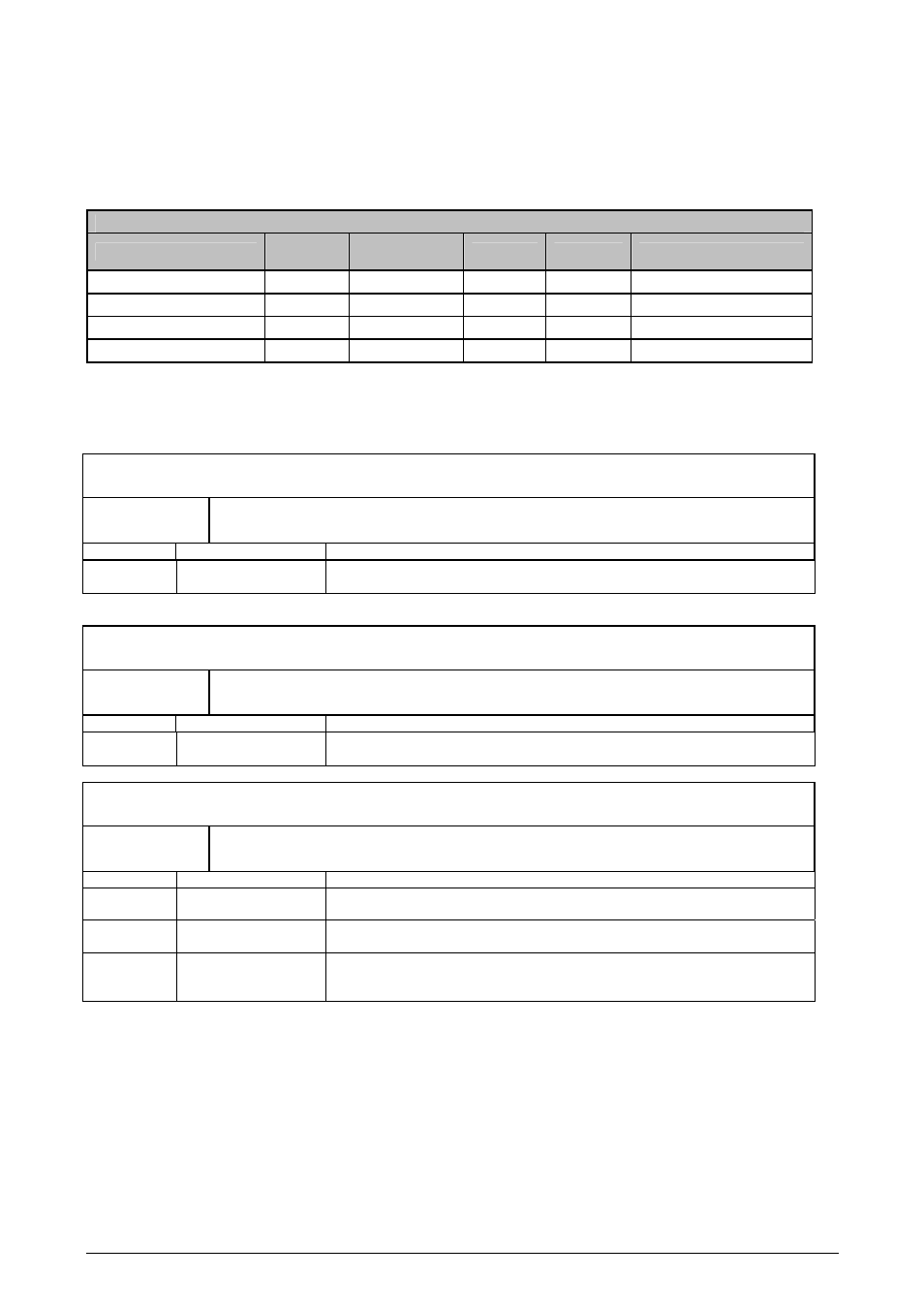

8.1 DMA Register Address Assignment

The DMA registers are 32 bits in width. The registers can be written to with 32-bit accesses only. Only the ARM946E-S

processor can access the registers.

DMA-Register

(Start 0x8000_0000)

Register Name

Offset

Address

Address

Area

Access

Default

Description

DMAC0_SRC_ADDR_REG

0x0000

4 bytes

R/W

0x00000000

DMA Start address register

DMAC0_DEST_ADDR_REG

0x0004

4 bytes

R/W

0x00000000

DMA target address register

DMAC0_CONTR_REG

0x0008

4 bytes

R/W

0x00000000

DMA control register

DMAC0_CONF_REG

0x000C

4 bytes

R/W

0x00000000

DMA configuration register

Table 32: Overview of DMA Registers

8.2

Description of DMA Registers

(DMAC0SrcAddrReg)

DMA-Source Address

W/R Addr.: 0x8000_0000 Default: 0x0000_0000

Description

Start address of the data block to be transferred by the DMA controller

Bit No.

Name

Description

31..0 START_ADDRESS

Start

address

Only word addresses are permitted; bits 0 and 1 are ignored

(DMAC0DestAddrReg)

DMA-Destination Address

W/R Addr.: 0x8000_0004 Default: 0x0000_0000

Description

Target address oft he data block to be transferred by the DMA controller

Bit No.

Name Description

31..0 DESTINATION_ADD

RESS

Target address

Only word addresses are permitted; bits 0 and 1 are ignored

(DMAC0ContrReg)

Channel Control (*)

W/R Addr.: 0x8000_0008 Default: 0x0000_0000

Description

To define the data block length.

31..24 Reserved

23..21 D_DELAY_EXTENTI

ON

Extends the D_Delay in number of 50 MHz clocks (see Channel Config)

20..16 S_DELAY_EXTENTI

ON

Extends the S_Delay in number of 50 MHz clocks (see Channel Config)

15..0 BYTE_COUNT

Number of bytes to be transferred. The byte count must be aligned with the

set bus width; that is, if a 32-bit byte count is set for the target or source, only

one 4-byte aligned byte count can be used.

Copyright © Siemens AG 2007. All rights reserved.

86

ERTEC 200 Manual

Technical data subject to change Version 1.1.0