Uart register description, Uartlcr_h, Uartlcr_m – Siemens ERTEC200 User Manual

Page 51: Uartlcr_l

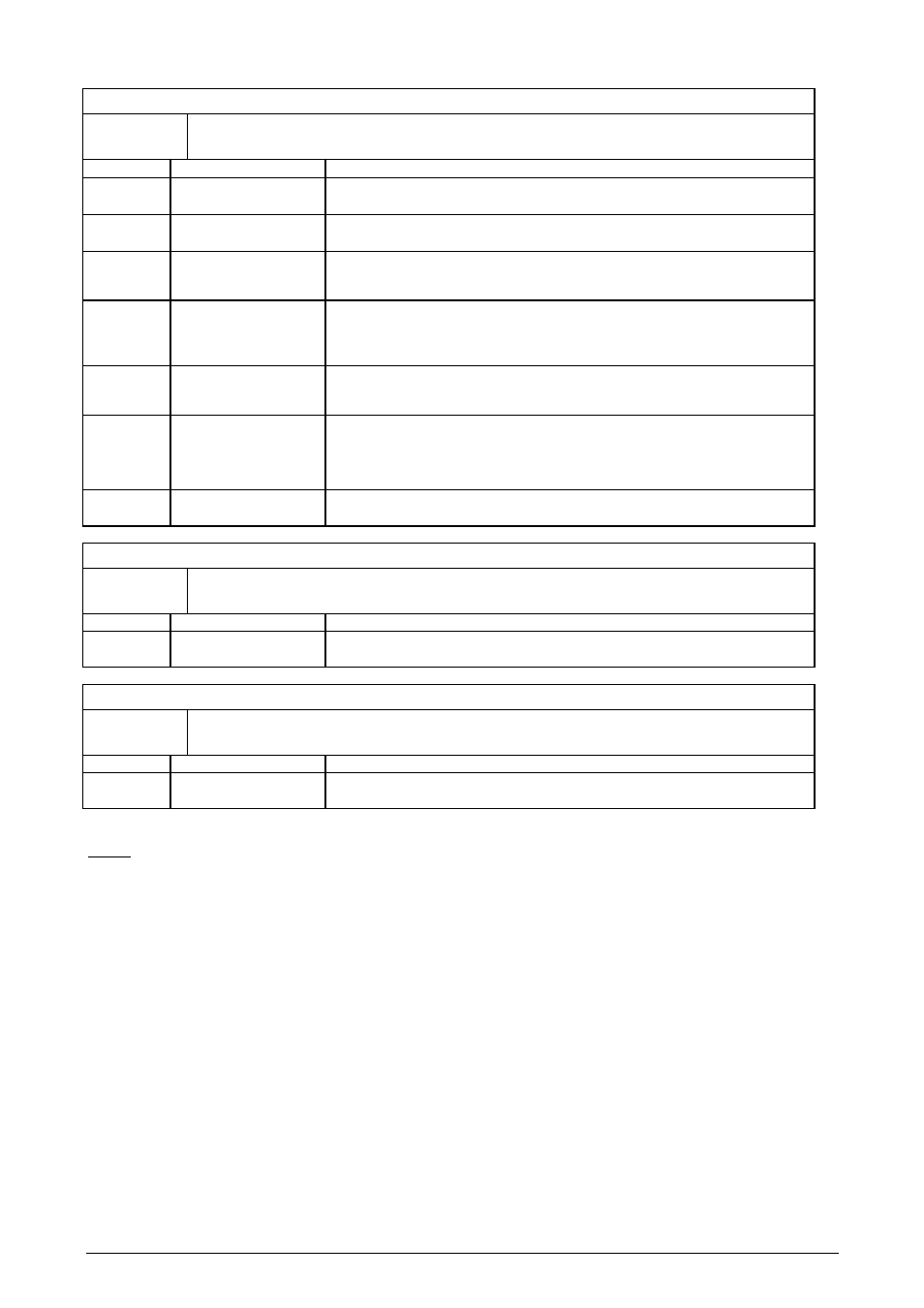

UARTLCR_H

R/W Addr.: 0x4000_2308 Default: 0x00

Description

UART line control register high byte bit rate and control register bits 22 to 16

Bit No.

Name

Description

0 BRK

Send break = 1 A LOW level is sent continuously at the Transmit output.

1 PEN

Parity enable = 1 Parity check and generation are enabled.

2 EPS

If PEN = 1

Even parity select = 1

Even parity (1) for check and generation.

Even parity select = 0

Odd parity (0) for check and generation.

3 STP2

Two stop bit select = 1 Two stop bits are appended at the end of the frame

when sending.

Two stop bit select = 0 One stop bit is appended at the end of the frame

when sending.

4 FEN

FIFO enable = 1 FIFO modes for sending and receiving are enabled.

FIFO enable = 0 FIFO is disabled. Sending/receiving is then performed via

1-byte holding registers.

6 – 5

WLEN

Word length indicates the number of data bits within a frame.

00 5-bit data

01 6-bit data

10 7-bit data

11 8-bit data

7 -------

Reserved

Value is undefined

UARTLCR_M

R/W Addr.: 0x4000_230C Default: 0x00

Description

UART line control register middle byte baud rate high byte bits 15 - 8

Bit No.

Name

Description

7 – 0

BAUD DIVMS

Baud rate divisor high byte

UARTLCR_L

R/W Addr.: 0x4000_2310 Default: 0x00

Description

UART line control register low byte baud rate low byte bits 7 - 0

Bit No.

Name

Description

7 – 0

BAUD DIVLS

Baud rate divisor low byte

NOTE: The baud rate divisor is calculated according to the following formula:

F

UARTCLK

BAUDDIV = ------------------------- - 1

16 * baud rate

Zero is not a valid divisor.

UARTLCR consists of 3 bytes. Writing of bytes is complete when UARTLCR_H has been written. If one of the first two

bytes is to be changed, UARTLCR_H must be written at the end following the change.

Example: Write UARTLCR_L and/or UARTLCR_M, write UARTLCR_H as acceptance.

Write UARTLCR_H only means write and accept UARTLCR_H bits.

Copyright © Siemens AG 2007. All rights reserved.

51

ERTEC 200 Manual

Technical data subject to change Version 1.1.0