F-timer function, 4 f-timer function – Siemens ERTEC200 User Manual

Page 43

4.4 F-Timer Function

An F-timer is integrated in the ERTEC 200 in addition to the system timers. This timer works independently of the system

clock and can be used for fail-safe applications, for example. The F-timer is triggered via the alternative “F_CLK” function

at the external “BYP_CLK” input. External triggering is not possible if the ARM946E-S is operated in a reserved test

mode (Config[4:3] = 11).

The following signal pins are available for the F-timer on the ERTEC 200.

•

External counter cable

1

F_CLK

Description of function:

The asynchronous input signal of the external independent time base is applied at a synchronization stage via the

BYP_CLK input pin (alternative F_CLK function). To rule out occurrences of metastable states at the counter input, the

synchronization stage is implemented with three flip-flop stages. The count pulses are generated in a series-connected

edge detection. All flip-flops run at the APB clock of 50 MHz.

The F_COUNTER_VAL register is reset using an asynchronous block reset or by writing the value 0x XXXX 55AA (X

means “don’t care) to the F-counter register “FCOUNT_RES”. The next count pulse sets the counter to 0xFFFF FFFF

and the counter is decremented at each additional count pulse. The FCOUNT_RES register is cleared again at the next

clock cycle.

The count value can be read out by a 32-bit read access. While an 8-bit or 16-bit read access is possible, it is not useful

because it can result in an inconsistency in the read count values.

Note on input frequency:

The maximum input frequency for the F-CLK is one-quarter of the APB clock. In the event of a quartz failure on the

ERTEC 200, a minimum output frequency between 40 and 90 MHz is set at the PLL. This yields a minimum APB-CLK

frequency of PLLOUT

min

40 MHz

/ 6 = 6.6666 MHz. To rule out a malfunction in the edge evaluation, the F-CLK can not

exceed APB-CLKmin 6.66 MHz/4 = 1.6666 MHz

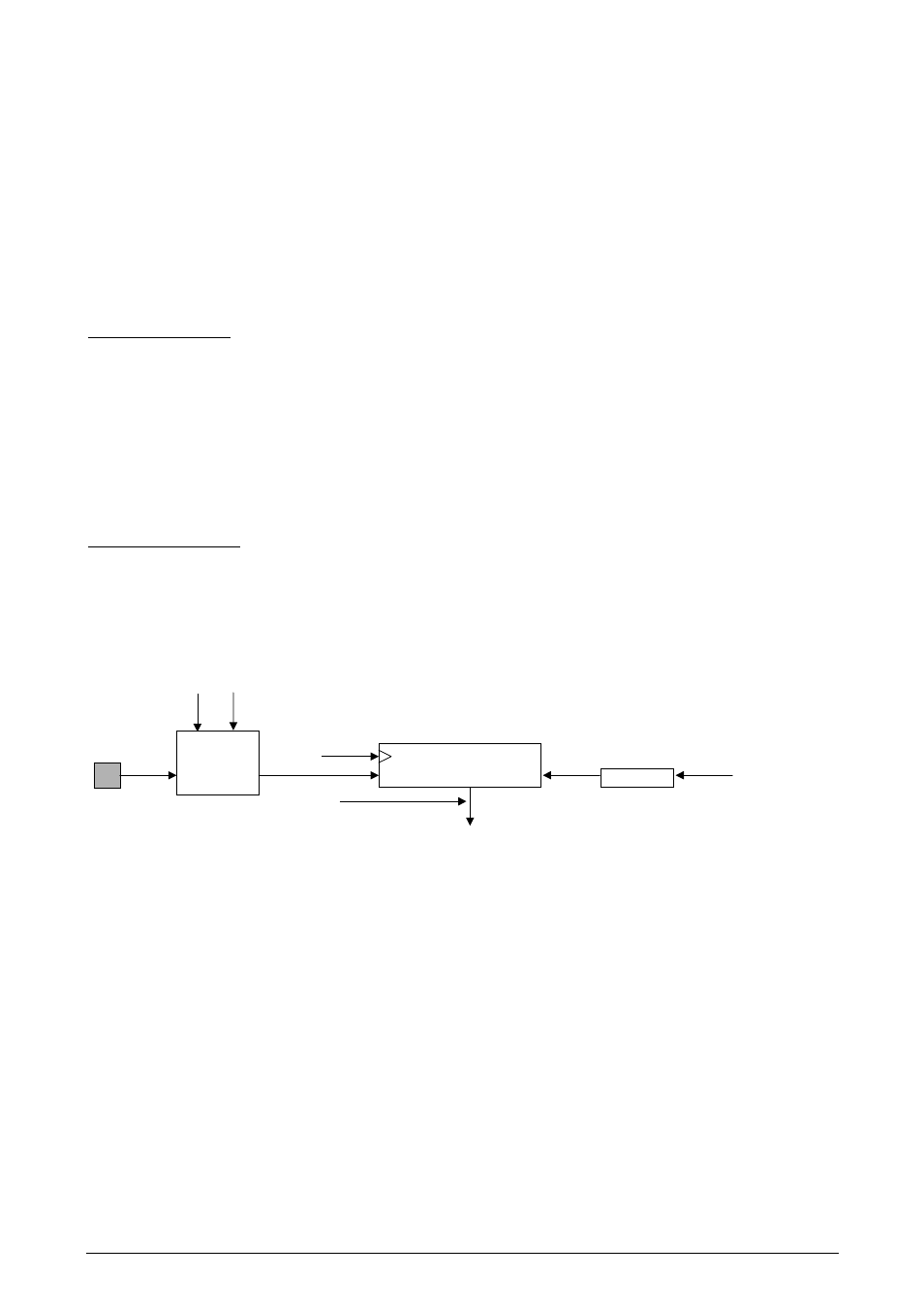

The figure below shows the function blocks of the F-counter.

32-Bit Down-Counter

F-Counter-Val(31:0)

F-COUNTER-EN

BYP_CLK

Sync Stage:

3 stages +

edge detect+

enable

DIRECT_IN

Read: F-Counter-Val

FCOUNT_RES

Reset

Write: F-Counter-Res

Data = 0xXXXX 55AAh

CLK APB

CLK_APB

EN

APB-Bus

F_CLK

CONFIG(4:3)

Figure 5: Block Diagram of F-Counter

Copyright © Siemens AG 2007. All rights reserved.

43

ERTEC 200 Manual

Technical data subject to change Version 1.1.0