Booting from external rom, Booting via spi, Booting via uart – Siemens ERTEC200 User Manual

Page 34: Booting via lbu, Memory swapping, I/o on apb bus, Boot rom, Table 7: access type and data width of the i/o

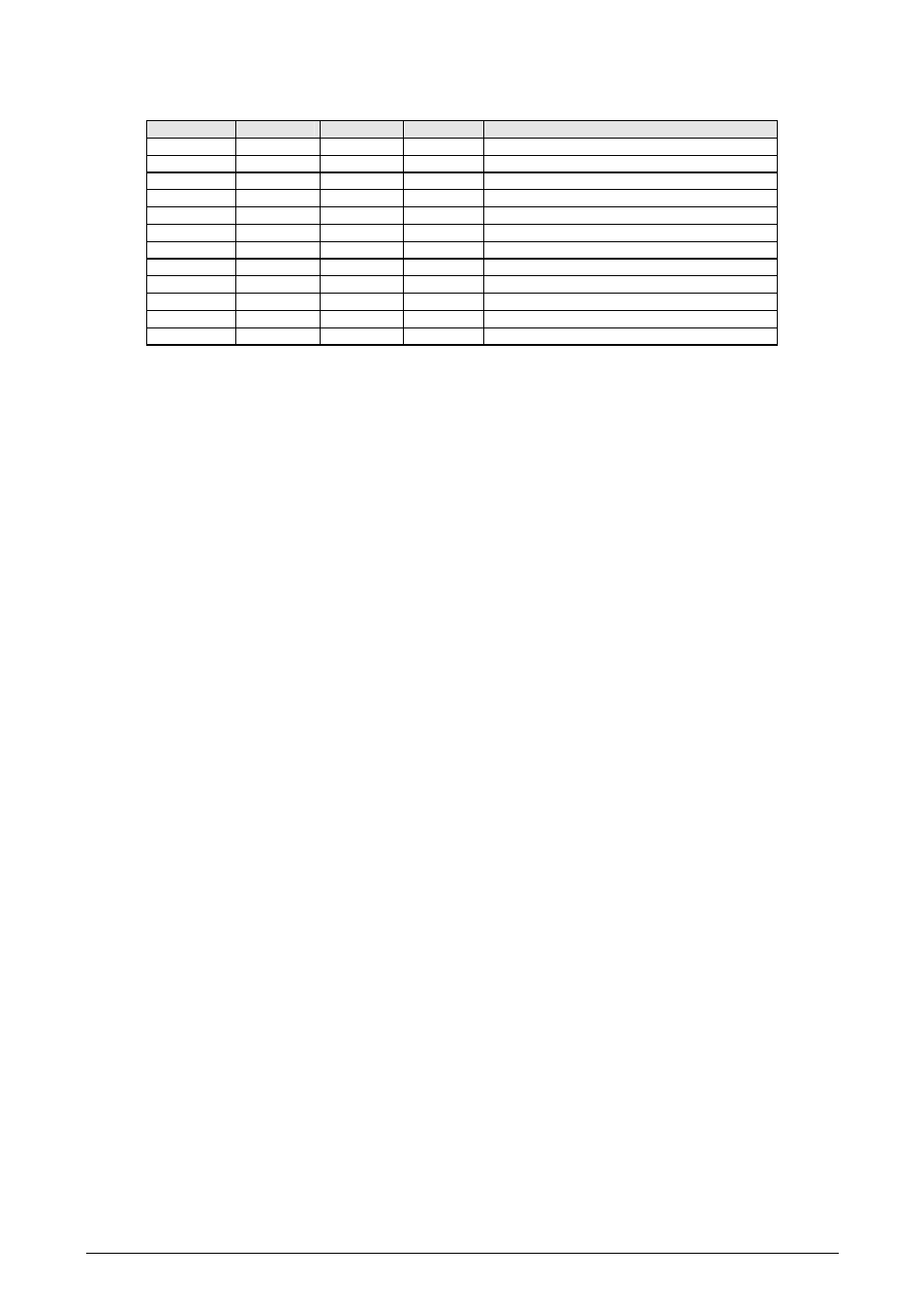

The following download modes are supported:

BOOT(3)

BOOT(2)

BOOT(1)

BOOT(0)

BOOTING OF

0

0

0

0

External ROM with 8-bit data width

0

0

0

1

External ROM with 16-bit data width

0

0

1

0

External ROM with 32-bit data width

1

0

0

0

Fast External ROM with 8-bit data width

1

0

0

1

Fast External ROM with 16-bit data width

1

0

1

0

Fast External ROM with 32-bit data width

0 0 1 1

Reserved

0 1 0 0

Reserved

0 1 0 1

SPI1

0 1 1 0

UART

0 1 1 1

LBU

1 0 1 1

Reserved

Table 8: Selection of Download Source

Booting from Flash or EEPROM with 8/16/32-bit data width via EMIF I/O Bank 0 (CS_PER0_N).

Booting from serial EEPROMs/Flashes via the SPI interface. The GPIO[22] control cable is used as the chip select

for the serial BOOT ROM. The storage medium is selected by means of the GPIO[23] control cable.

Booting from a host processor system via the LBU bus. In this case, the code is downloaded from the host

processor.

Booting from UART. With the bootstrap method, a routine for operation of the serial interface is first downloaded.

This routine then controls the actual program download.

4.1.1

Booting from External ROM

This boot mode is provided for applications for which the majority of the user firmware runs on the ARM946E-S. The boot

process is determined entirely by the external image. Thus, the boot process can be carried out with a minimum

initialization.

4.1.2 Booting

via

SPI

SPI-compatible EEPROMs as well as SPI-compatible Data Flash memories can be used as an SPI source. GPIO cable

GPIO[23] is used to select the type.

•

GPIO[23] = 0

Æ

SPI-compatible Data Flash

e.g., AT45DB011B

•

GPIO[23] = 1

Æ SPI-compatible

EEPROM

e.g., AT25HP256

The GPIO[22] GPIO cable is used as the chip select for the SDI memory.

The serial protocols by Motorola, Texas Instruments, and NSC are supported in principle.

4.1.3 Booting

via

UART

Boot mode via UART uses a bootstrap method that first downloads to the ERTEC200 a routine for operating the serial

interface, which then performs the actual download of the program.

After the boot operation, the UART interface can be used in a different capacity (e.g., as a terminal interface).

4.1.4 Booting

via

LBU

Booting via the LBU interface must be carried out actively by the external host processor. The LBU host can then transfer

the user code to the memory of the ERTEC 200.

The ARM boot software for booting via LBU does not read out any module ID. The module ID must be stored in a

memory medium (e.g. SPI-EEPROM) read out by the host processor via the LBU interface. Depending on the ID, the

host processor starts its boot process with the appropriate user software.

4.1.5 Memory

Swapping

The reset vector of the ARM946E-S points to address 0x0000_0000. For this reason, the boot ROM is placed starting at

address 0x0000_0000 after RESET. The boot ROM can also be addressed in its mirror area (see Section 10.2).When

the boot operation is complete, SRAM or SDRAM can be swapped to address 0x0000_0000 in order to create the

exception vector table for the ARM946E-S starting from address 0x0000_0000 - 0x0000_001F. The original address

areas for boot ROM, SRAM, and SDRAM are not affected by memory swapping.

Memory swapping takes place in the MEM-SWAP system control register.

Copyright © Siemens AG 2007. All rights reserved.

34

ERTEC 200 Manual

Technical data subject to change Version 1.1.0