Phy_ status, Uart_clk – Siemens ERTEC200 User Manual

Page 63

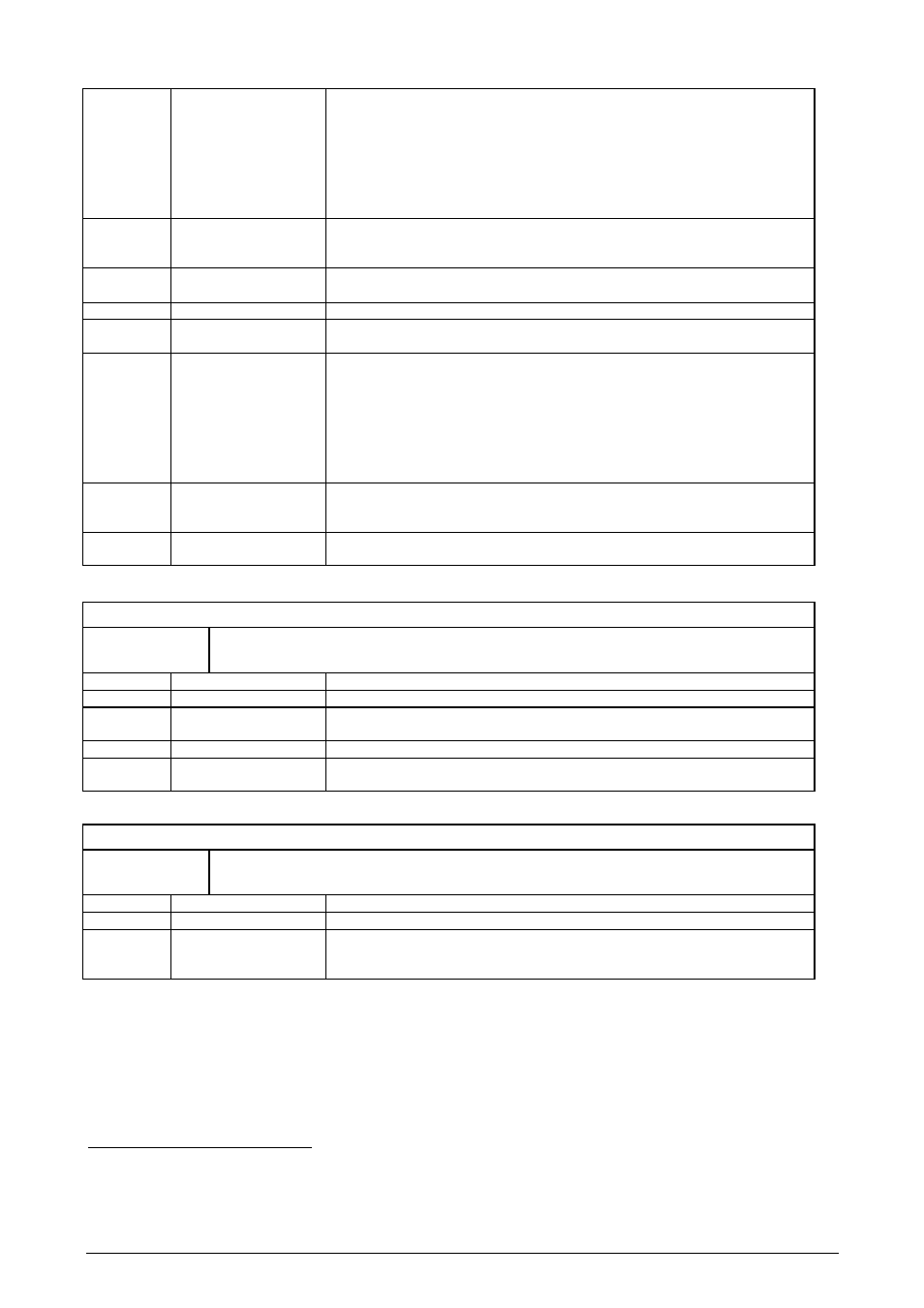

12:10

P2_PHY_MODE

000: 10BASE-T HD, Auto-Neg disabled

001: 10BASE-T FD, Auto-Neg disabled

010: 100BASE-TX/FX HD, Auto-Neg disabled

011: 100BASE-TX/FX FD, Auto-Neg disabled

100: 100BASE-TX HD announced, Auto-Neg enabled

101: 100BASE-TX HD announced, Auto-Neg enabled, Repeater Mode

110: PHY starts in Power Down Mode

111: Auto-Neg enabled, AutoMDIX enabled, everything is possible

9

P2_FX_ MODE

1: The 100BASE-FX Interface is enabled

(only meaningful when P2_PHY_Mode =“010“ or “011“)

0: The 100BASE-FX Interface is disabled

8

P2_PHY_ENB

0: PHY2 disabled (Powerdown Mode)

1: PHY2 enabled

7:6

Reserved

5

P1_AUTOMDIXEN

1: Enable AutoMDIX state machine

0: Disable AutoMDIX state machine

4:2

P1_PHY_ MODE

000: 10BASE-T HD, Auto-Neg disabled

001: 10BASE-T FD, Auto-Neg disabled

010: 100BASE-TX/FX HD, Auto-Neg disabled

011: 100BASE-TX/FX FD, Auto-Neg disabled

100: 100BASE-TX HD announced, Auto-Neg enabled

101: 100BASE-TX HD announced, Auto-Neg enabled, Repeater Mode

110: PHY starts in Power Down Mode

111: Auto-Neg enabled, AutoMDIX enabled, everything is possible

1

P1_FX_ MODE

1: The 100BASE-FX interface is enabled

(only meaningfule when P1_PHY_Mode =“010“ or “011“)

0: The 100BASE-FX interface is disabled

0

P1_PHY_ENB

0: PHY1 disabled (Powerdown Mode)

1: PHY1 enabled

PHY_ STATUS

R Addr.:

0x4000_2660

Default: 0x0000_0000

Description

Status of PHY1 and PHY2

Bit No.

Name

Description

31:9

Reserved

8

P2_PWRUPRST

0: PHY2 in Powerdown mode or internal reset is still active

1: PHY2 is ready for operation

7:1

Reserved

0 P1_PWRUPRST

0: PHY1 in Powerdown mode or internal reset is still active

1: PHY1 is ready for operation

UART_CLK

R/W

Addr.: 0x4000_2670 Default: 0x0000_0000

Description

Enables switching of the UART clock from 50 MHz (default) to 6 MHz. At 6 MHz, a UART baud

rate of 187.5 kBd is possible.

Bit No.

Name

Description

31:1 Reserved

Reserved

0 UART_TAKT

UART

clock:

0: 50 MHz

1: 6 MHz

2

If the PHY is 'Disabled' and then 'Enabled' again, a Disable Time of > 100

µs must be adhered to by the SW.

3

P1/2_PHYENABLE = 1 triggers a reset extension internally in PHY beyond 5.2 ms. During this time, the PLL and all

analog and digital components are powered up. The ready to operate status is signaled in the PHY_Status-Register with

P1/2_PWRUPRST = 1.

Copyright © Siemens AG 2007. All rights reserved.

63

ERTEC 200 Manual

Technical data subject to change Version 1.1.0