Uart register description, Address assignment of uart registers, Table 13: baud rates for uart at f – Siemens ERTEC200 User Manual

Page 50: Uartclk, 50 mhz, Table 14: overview of uart registers, Uartdr, Uartrsr/uartecr

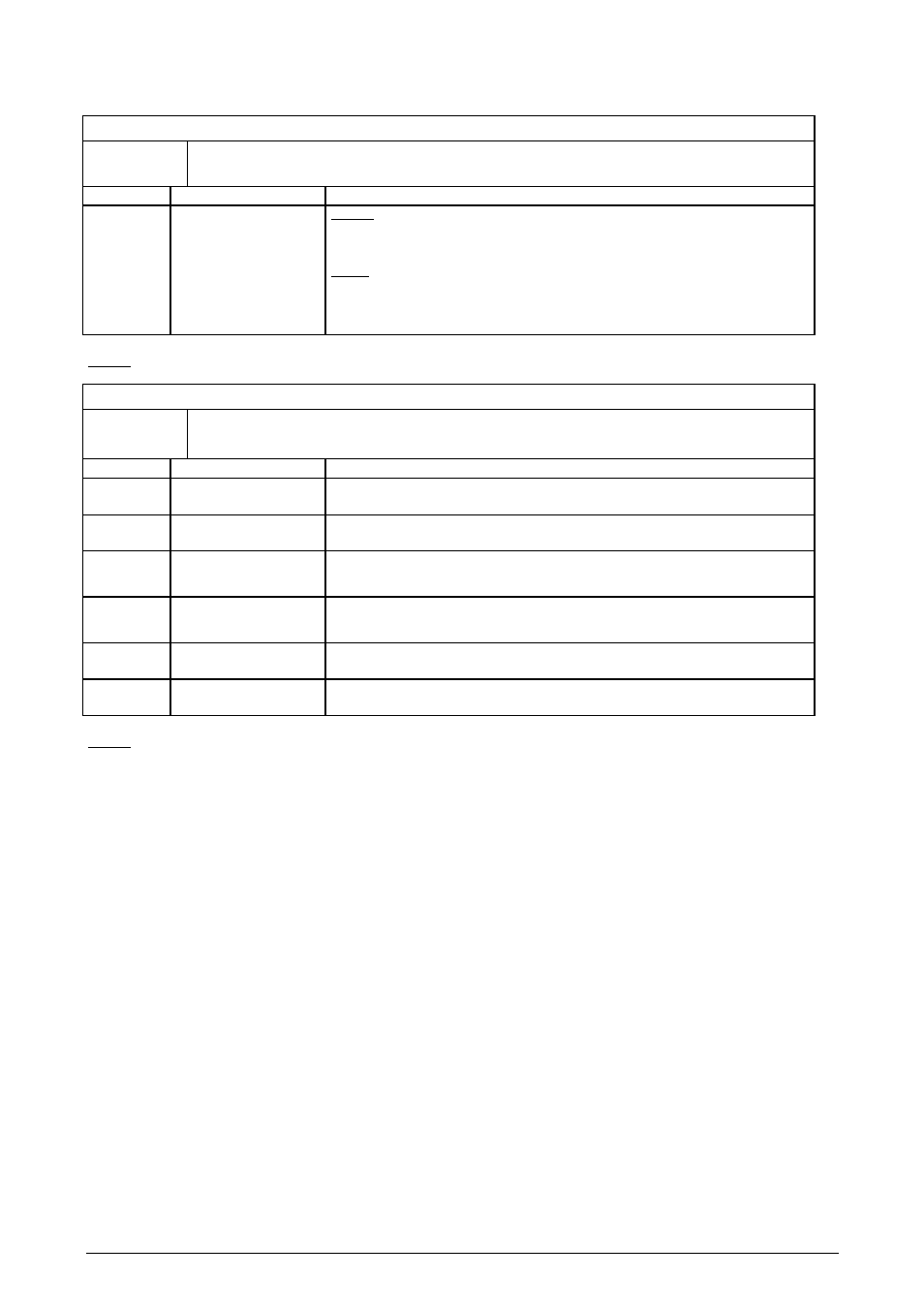

4.6.2

UART Register Description

UARTDR

R/W

Addr.: 0x4000_2300 Default: 0x--

Description

UART data registers

Bit No.

Name

Description

7 – 0

-------

WRITE:

-

If FIFO is enabled, the written data are entered in the FIFO.

-

If FIFO is disabled, the written data are entered in the Transmit holding register

(the first word in the Transmit FIFO).

READ:

-

If FIFO is enabled, the received data are entered in the FIFO.

-

If FIFO is disabled, the received data are entered in the Receive holding register

(the first word in the RECEIVE FIFO).

NOTE: When data are received, the UARTDR data register must be read out first and then the UARTRSR error register.

UARTRSR/UARTECR

R/W Addr.: 0x4000_2304 Default: 0x00

Description

UART receive status register (read)

UART receive error clear register (write)

Bit No.

Name

Description

7 – 0

------- (Write)

Framing errors, parity errors, break errors, and overrun errors are deleted.

0

FE (Read)

Framing error = 1

Received character does not have a valid stop bit

1

PE (Read)

Parity error = 1

Parity of received character does not match the assigned parity in

the UARTLCR_H register Bit 2.

2

BE (Read)

Break error = 1

A break was detected. A break means that the received data are at

LOW for longer than a standard character with all control bits.

3

OE (Read)

Overrun-Error = 1

If the FIFO is full and a new character is received.

7 – 4

------- (Read)

Reserved

Value is undefined

NOTE: When new data are displayed, the UARTDR data register must be read out first and then the UARTRSR error

register. The error register is not updated until the data register is read.

Copyright © Siemens AG 2007. All rights reserved.

50

ERTEC 200 Manual

Technical data subject to change Version 1.1.0