Host interrupt handling – Siemens ERTEC200 User Manual

Page 82

7.5.4

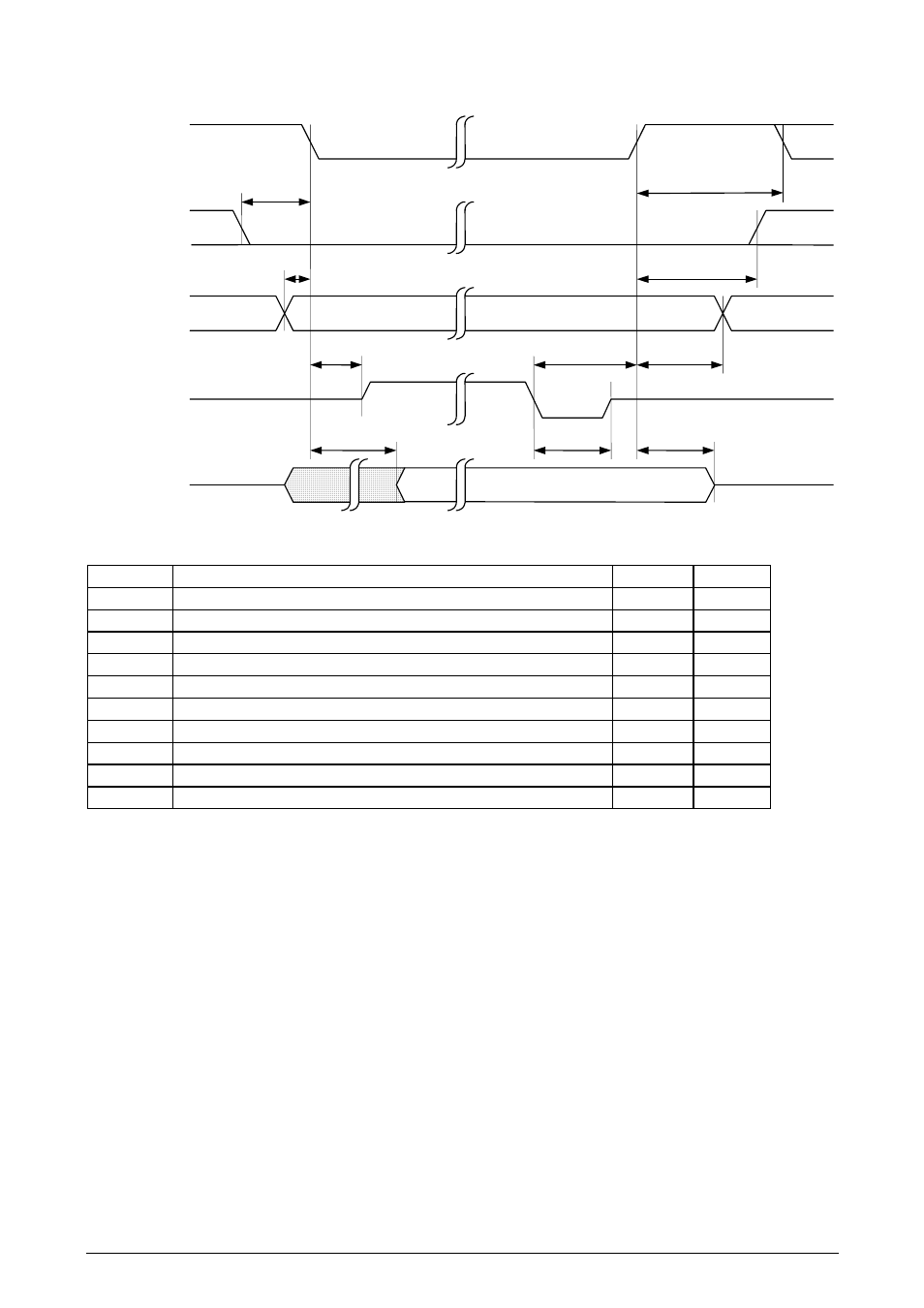

LBU Write to ERTEC 200 with common Read/Write line (LBU_RDY_N active low)

LBU_CS_R_N/

LBU_CS_M_N

LBU_WR_N

LBU_A(20:0)/

LBU_SEG(1:0)/

LBU_BE(1:0)_N

LBU_RDY

LBU_D(15:0)

t

WCS

t

ACS

t

CRE

t

CDV

t

CDH

t

CAH

t

CWH

t

RTC

t

RAP

t

WR

Figure 16: LBU-Write-Sequence with common RD/WR line

Parameter Description

Min

Max

t

WCS

write signal asserted to chip select setup time

2 ns

1

t

ACS

address valid to chip select asserted setup time

0 ns

t

CRE

chip select asserted to ready enabled delay

5 ns

12 ns

t

CDV

chip select asserted to data valid delay

40 ns

t

RAP

ready active pulse width

17 ns

23 ns

t

CWH

write signal deasserted to chip select deasserted hold time

0 ns

t

CAH

address valid to chip select deasserted hold time

0 ns

t

RTC

ready asserted to chip select deasserted delay

0 ns

t

CDH

data valid/enabled to chip select deasserted hold time

0 ns

t

WR

write recovery time

25 ns

Table 28: LBU Write access timing with common Read/Write line

1

The setup time

t

WCS

must be maintained under all circumstances; otherwise the LBU unit drives the ERTEC 200

databus.

The ERTEC 200 has two LBU chip select inputs. One for access to the page configuration register (LBU_CS_R_N) and

one to access to the ERTEC 200 memory address space (LBU_CS_M_N). Only one of these chip select signals may be

active at a time and it is not allowed to change the chip select during the complete access.

7.6 Host Interrupt Handling:

The ERTEC 200 generates 2 interrupt signals, LBU_IRQ0_N and LBU_IRQ1_N, to the external host. Both interrupts are

generated in the IRT switch interrupt controller. Both signals are set by default to Low Active. However, they can also be

assigned different parameters in the IRT switch.

Mailbox handling between the ARM946E-S and an external host is possible via the IRT switch interrupt controller.

An interrupt request from the ARM946E-S to the host processor is initiated by writing to the Activate_HP_Interrupt

register.

An interrupt request from the host processor to the ARM946E-S is initiated by writing to the Activate_SP_Interrupt

register.

Both registers can only be written to. Any value can be written.

Copyright © Siemens AG 2007. All rights reserved.

82

ERTEC 200 Manual

Technical data subject to change Version 1.1.0