System control register description, Table 16: overview of system control registers, Pll_stat_reg – Siemens ERTEC200 User Manual

Page 60: Qvz_ahb_adr, Qvz_ahb_ctrl

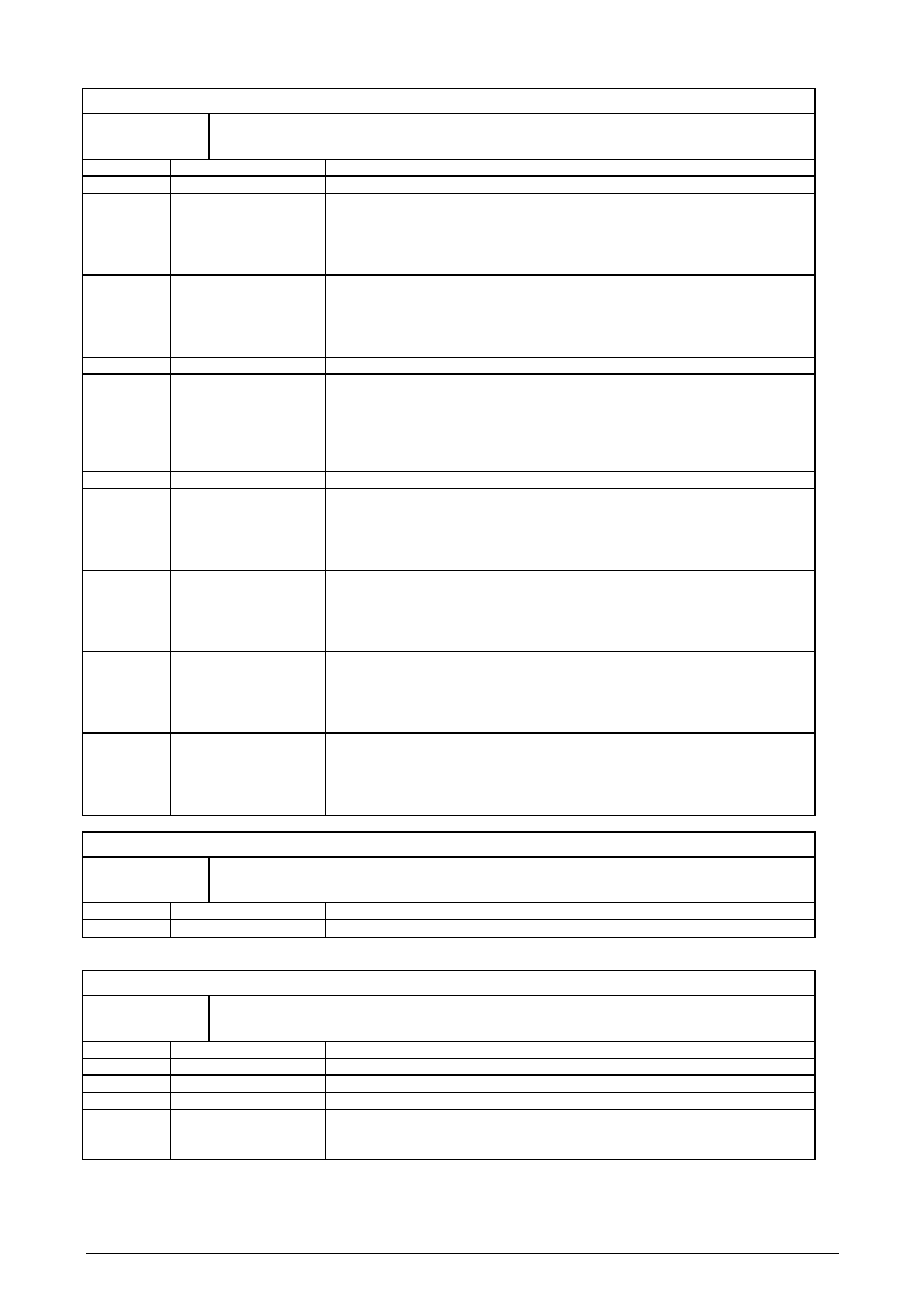

PLL_STAT_REG

R/W

Addr.:

0x4000_2614

Default: 0x0007_0005

Description

Status register for PLL of ERTEC 200 and interrupt control for FIQ3

Bit No.

Name

Description

31..18 Reserved

Reserved

17

INT_MASK_LOSS

INT_MASK_LOSS:

Interrupt masking for INT_LOSS_STATE

0: Interrupt is enabled

1: Interrupt is masked

Read/write accessible

16

INT_MASK_LOCK

INT_MASK_LOCK:

Interrupt masking for INT_LOCK_STATE

0: Interrupt is enabled

1: Interrupt is masked

Read/write accessible

15..6 Reserved

Reserved

5

INT_QVZ_EMIF_

STATE

Interrupt timeout at EMIF (INT_QVZ_EMIF_

STATE):

0: Interrupt request is inactive

1: Interrupt request is active

Read access only;

This bit represents the value of Bit 7 of EMIF register Extended_Config.

4 Reserved

Reserved

3

INT_LOSS_STATE

Interrupt loss state (INT_LOSS_STATE):

0: Interrupt request is inactive

1: Interrupt request is active

This bit indicates whether the PLL input clock has failed (latching).

Read/write accessible

2

INT_LOCK_STATE

Interrupt lock state (INT_LOCK_STATE):

0: Interrupt request is inactive

1: Interrupt request is active

This bit indicates whether the PLL was in unlocked state (latching).

Read/write accessible

1

PLL_INPUT_CLK_LO

SS

Loss: Monitoring status of PLL input clock

1: PLL input clock not detected

0: PLL input clock available

This bit indicates the current monitoring status of the PLL input clock.

Read access only

0

PLL_LOCK

Lock: Engages at operating frequency; status of PLL:

0: PLL is unlocked

1: PLL is locked

This bit represents the current lock state of the PLL.

Read access only

QVZ_AHB_ADR

R Addr.:

0x4000_2628

Default: 0x0000_0000

Description

Address of incorrect addressing on multilayer AHB

Bit No.

Name

Description

31:0 QVZ_AHB_ADR

Address

QVZ_AHB_CTRL

R

Addr.: 0x4000_262C

Default: 0x0000_0000

Description

Control signals of an incorrect addressing on the multi-layer AHB

Bit No.

Name

Description

31:7 Reserved

Reserved

6:4 HBURST

HBURST

3:1 HSIZE

HSIZE

0

HWRITE

HWRITE

0: HREAD

1: HWRITE

Copyright © Siemens AG 2007. All rights reserved.

60

ERTEC 200 Manual

Technical data subject to change Version 1.1.0