Clock and reset, Test pins, Emif (external memory interface) – Siemens ERTEC200 User Manual

Page 14: Jtag and debug, Trace port

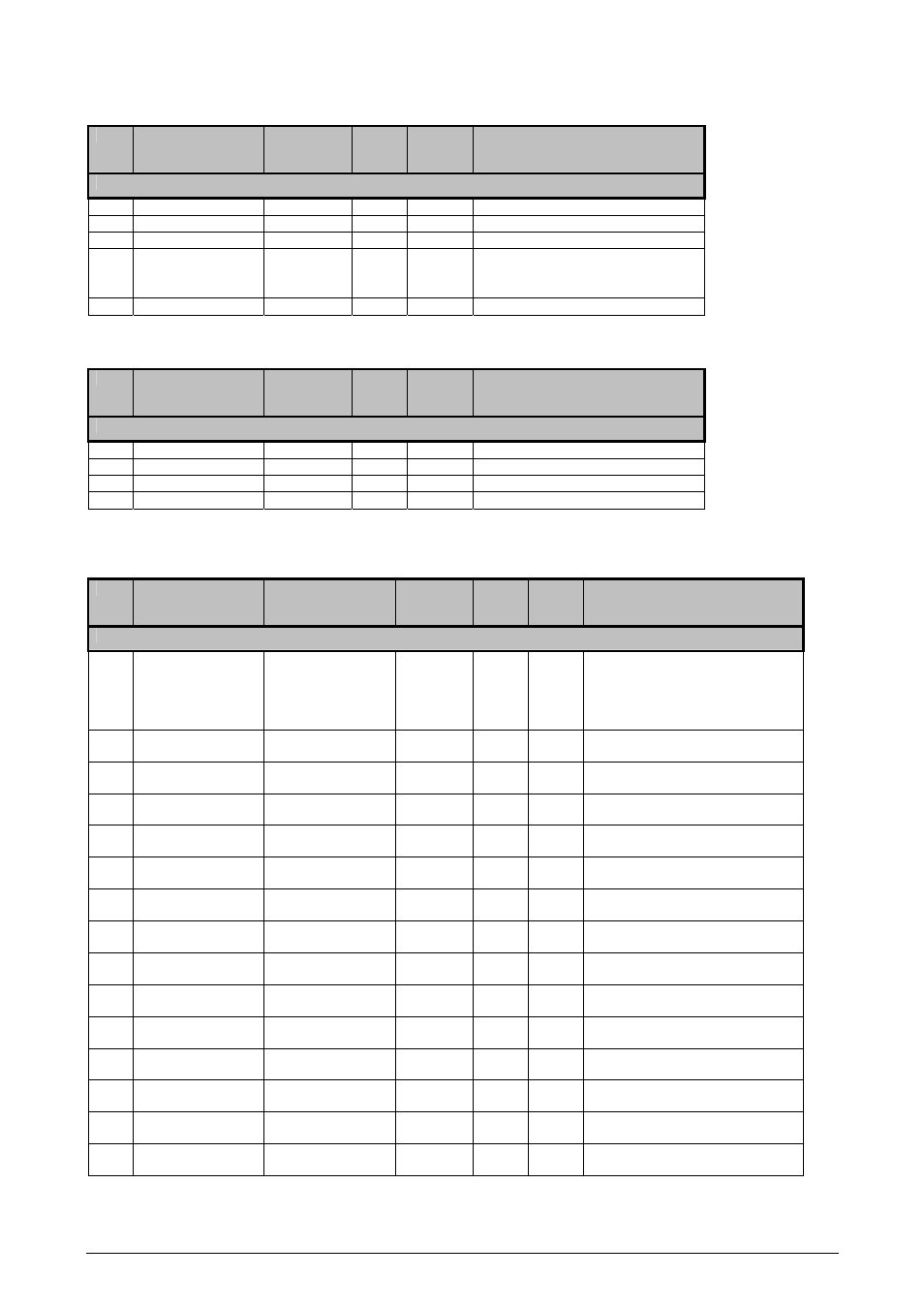

1.5.4

Clock and Reset

No.

Signal Name

I/O

(Reset)

Pull-

PIN

No.

Comment

CLOCK / RESET GENERATION

42 CLKP_A

I (I)

B14

Quartz connection

43 CLKP_B

O

D14

Quartz connection

44 F_CLK

I (I)

B13

F_CLK for F-counter

45 REF_CLK

Dependent

on PIN

CONFIG[1]

A15

Tristate or

reference clock output, 25 MHz

46 RESET_N

I (I)

up

B7

PowerOn reset

1.5.5 Test

Pins

No.

Signal Name

I/O

(Reset)

Pull-

PIN

No.

Comment

TEST

47

TEST_N (3)

I (I)

up

T5

Test mode

48

TMC1 (3)

I (I)

G5

Test configuration

49

TMC2 (3)

I (I)

H6

Test configuration

50

TACT_N (3)

I (I)

dn

J5

TESTACT-TAP reset

1.5.6

EMIF (External Memory Interface)

No.

Signal Name

Alternative

Reset Function

I/O

(Reset)

Pull-

PIN

No.

Comment

EMIF (External Memory Interface)

51 DTR_N

BOOT0

B (I)

up

E7

Direction signal for external driver

or scan clock (Scan mode)

ERTEC 200 boot mode (external

PD may be necessary)

52 OE_DRIVER_N

O (O)

D8

Enable signal for external driver

or scan clock (Scan mode)

53 A0

O (O)

B4

Address bit 0

SDRAM: Bank address 0

54 A1

O (O)

A3

Address bit 1

SDRAM: Bank address 1

55 A2

O (O)

B3

Address bit 2

SDRAM: Address 0

56 A3

O (O)

B2

Address bit 3

SDRAM: Address 1

57 A4

O (O)

D4

Address bit 4

SDRAM: Address 2

58 A5

O (O)

C2

Address bit 5

SDRAM: Address 3

59 A6

O (O)

C1

Address bit 6

SDRAM: Address 4

60 A7

O (O)

D2

Address bit 7

SDRAM: Address 5

61 A8

O (O)

D1

Address bit 8

SDRAM: Address 6

62 A9

O (O)

E2

Address bit 9

SDRAM: Address 7

63 A10

O (O)

E1

Address bit 10

SDRAM: Address 8

64 A11

O (O)

F2

Address bit 11

SDRAM: Address 9

65 A12

O (O)

F1

Address bit 12

SDRAM: Address 10

Copyright © Siemens AG 2007. All rights reserved.

14

ERTEC 200 Manual

Technical data subject to change Version 1.1.0