Async bank 0 config, Async bank 1 config, Async bank 2 config – Siemens ERTEC200 User Manual

Page 72: Async bank 3 config

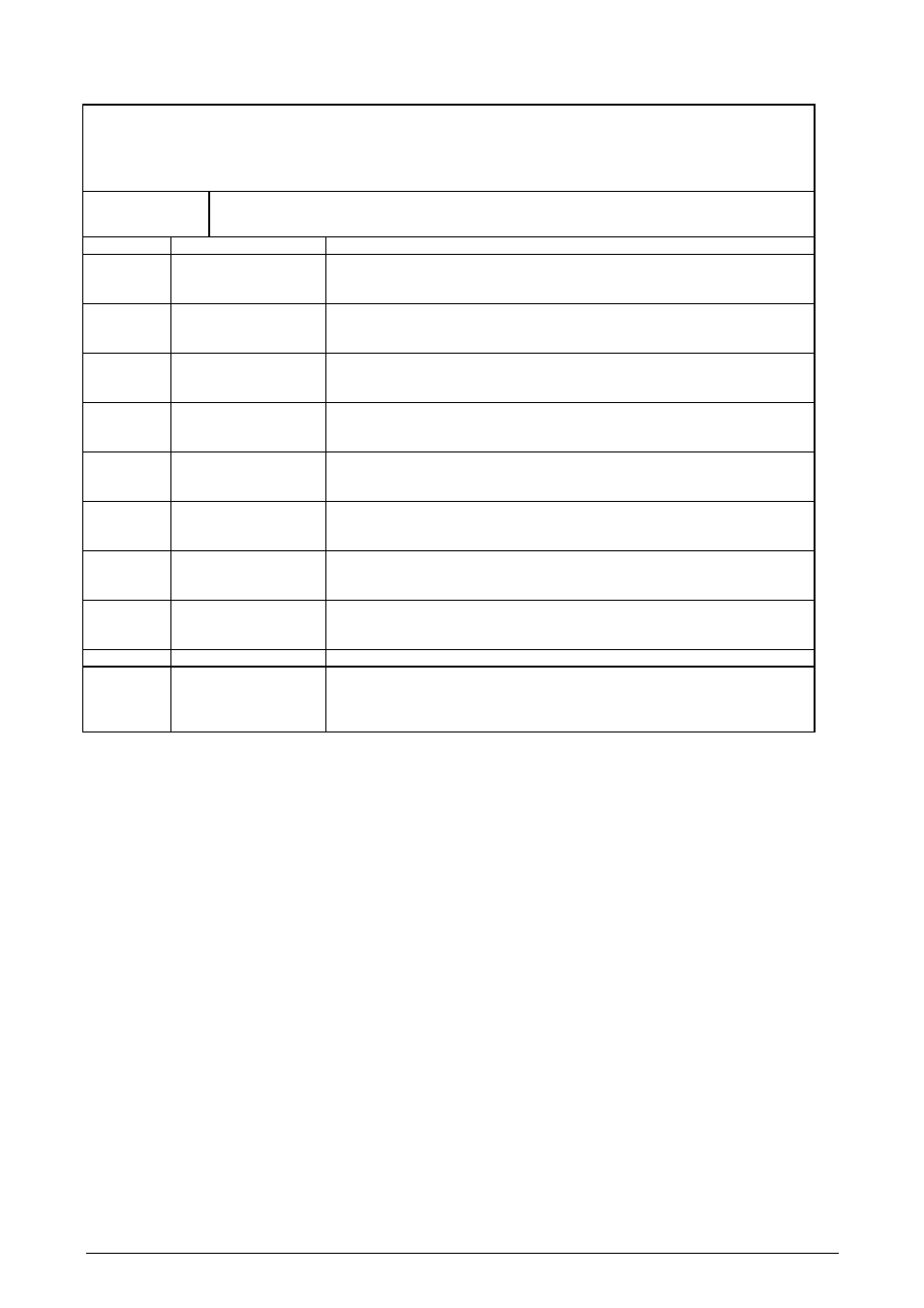

Async Bank 0 Config

W/R Addr.: 0x7000_0010 Default: 0x3FFF_FFF2

Async Bank 1 Config

W/R Addr.: 0x7000_0014 Default: 0x3FFF_FFF2

Async Bank 2 Config

W/R Addr.: 0x7000_0018 Default: 0x3FFF_FFF2

Async Bank 3 Config

W/R Addr.: 0x7000_001C Default: 0x3FFF_FFF2

Description

Setting of timing and data bus width for access via asynchronous interface CS_PER0_N -

CS_PER3_N. (The AHB clock is 20 ns in length)

Bit No.

Name

Description

31

EWS_XAS

Extend Wait Timing Mode

0: RDY_PER_N = asynchronous

1: RDY_PER_N = synchronous

30

EW

Extend Wait mode

0: RDY_PER_N = don’t care

1: Wait until RDY_PER_N is active

29..26

W_SU

Write strobe setup cycles

(w_su + 1) AHB clock cycles between valid address, data, and chip select

and falling edge of the write signal.

25..20

W_STROBE

Write strobe duration cycles

(w_strobe + 1) AHB clock cycles between falling and rising edges of the write

signal.

19..17

W_HOLD

Write strobe hold cycles

(w_hold + 1) AHB clock cycles between rising edge of the write signal and

change of address, data, and chip select.

16..13

R_SU

Read strobe setup cycles

(r_su + 1) AHB clock cycles between valid address and chip select and

falling edge of the read signal (RD_N).

12..7

R_STROBE

Read strobe duration cycles

(r_strobe + 1) AHB clock cycles between falling and rising edges of the read

signal.

6..4

R_HOLD

Read strobe hold cycles

(r_hold + 1) AHB clock cycles between rising edge of the read signal and

change of address and chip select.

3..2 Reserved

Reserved

1..0

ASIZE

Asynchronous bank size

00: 8-bit data bus

01: 16-bit data bus

1x: 32-bit data bus

Copyright © Siemens AG 2007. All rights reserved.

72

ERTEC 200 Manual

Technical data subject to change Version 1.1.0