Input/output ports, Mode registers – Zilog Z86193 User Manual

Page 50

Z8

®

CPU

User Manual

UM001604-0108

Input/Output Ports

43

Input/Output Ports

Z8

®

CPU features up to 32 lines dedicated to input and output. These lines are grouped

into four 8-bit ports known as Port 0, Port 1, Port 2, and Port 3. Port 0 is nibble program-

mable as input, output, or address. Port 1 is byte configurable as input, output, or address/

data. Port 2 is bit programmable as either inputs or outputs, with or without handshake and

SPI. Port 3 can be programmed to provide timing, serial and parallel input/output, or com-

parator input/output.

All ports have push–pull CMOS outputs. In addition, the push–pull outputs of Port 2 can

be turned OFF for open-drain operation.

Mode Registers

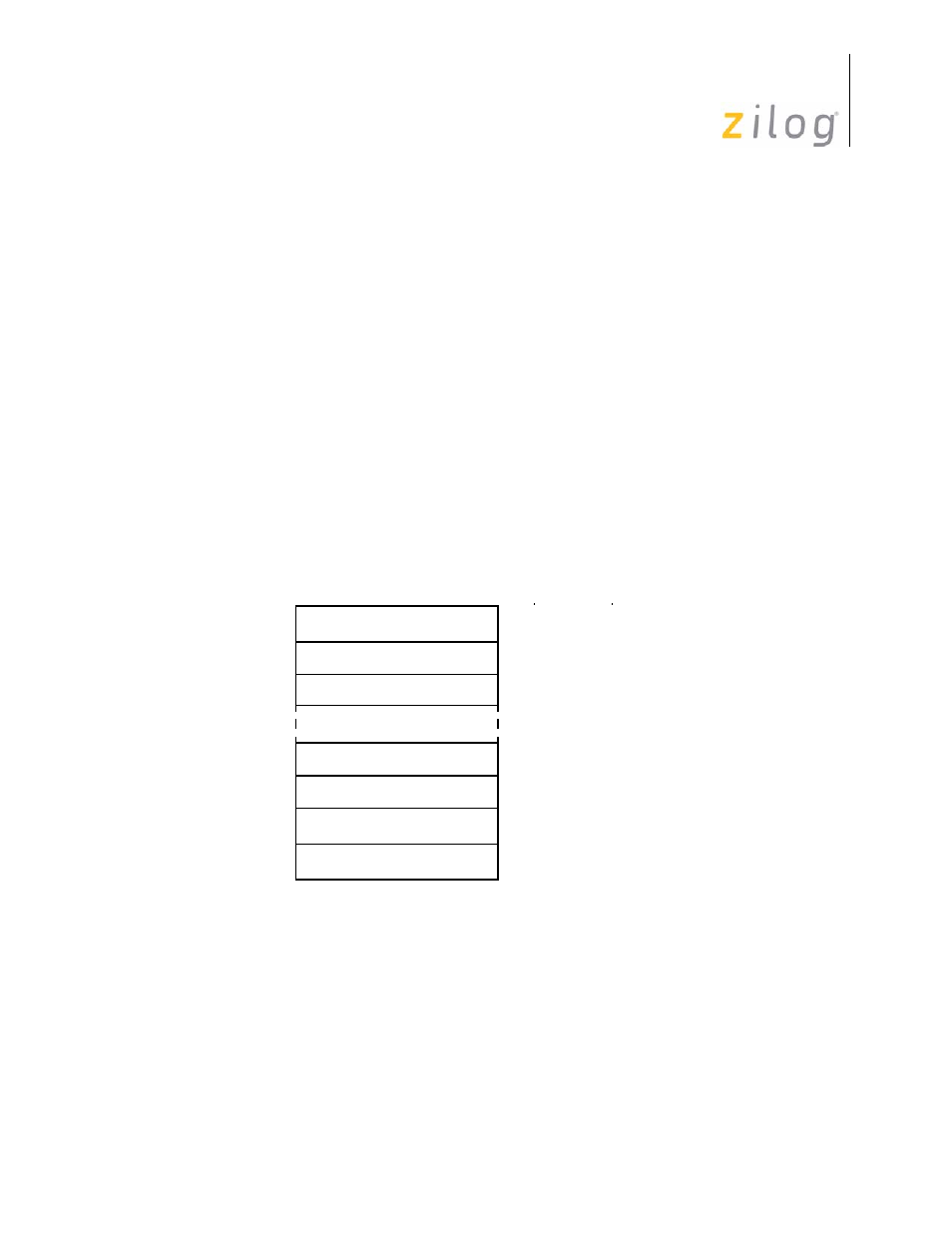

Each port has an associated Mode Register that determines the port’s functions and allows

dynamic change in port functions during program execution. Port and Mode Registers are

mapped into the Standard Register File as displayed in

Because of their close association, Port and Mode registers are treated like any other gen-

eral-purpose registers. There are no special instructions for port manipulation. Any

instruction which addresses a register can address the ports. Data can be directly accessed

in the Port Register, with no extra moves.

Figure 28. I/O Ports and Mode Registers

Register

HEX

Port 3 Mode

Port 2 Mode

Identifier

F8h

F7h

F6h

P01M

P3M

P2M

Port 3

Port 0–1 Mode

Port 2

Port 1

Port 0

03h

02h

01h

00h

P3

P2

P1

P0

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003