Zilog Z86193 User Manual

Page 15

Z8

®

CPU

User Manual

UM001604-0108

Address Space

8

With 4-bit addressing, the register file is logically divided into 16 Working Register

Groups of 16 registers each, as listed in

. These 16 registers are known as Working

Registers. A Register Pointer (one of the control registers,

FDh

) contains the base address

of the active Working Register Group. The high nibble of the Register Pointer determines

the current Working Register Group.

When accessing one of the Working Registers, the 4-bit address of the Working Register is

combined within the upper four bits (high nibble) of the Register Pointer, thus forming the

8-bit actual address.

on page 9 displays this operation. Because working registers

are typically specified by short format instructions, there are fewer bytes of code required,

which reduces execution time. In addition, when processing interrupts or changing tasks,

the Register Pointer speeds context switching. A special Set Register Pointer (SRP)

instruction sets the contents of the Register Pointer.

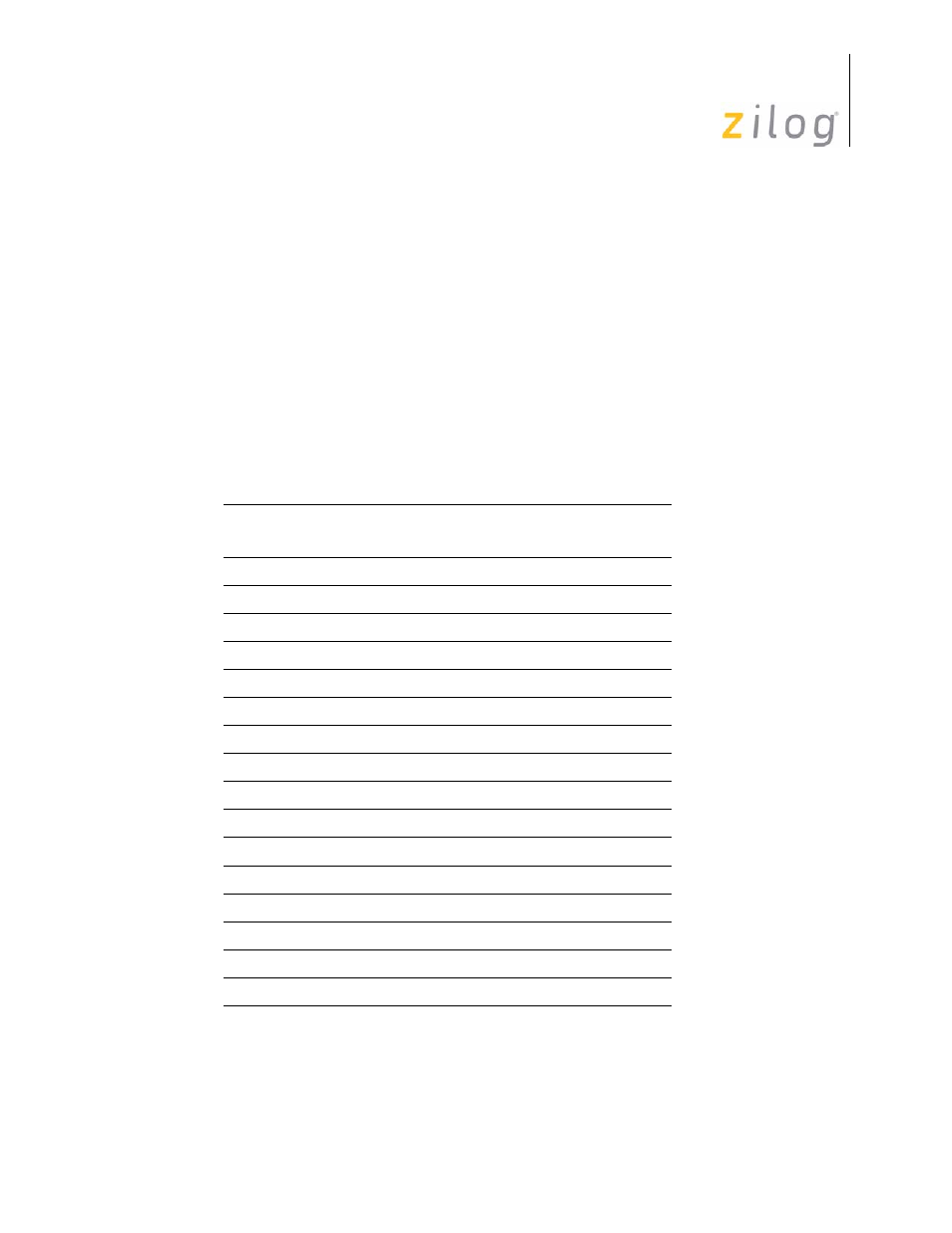

Table 3. Working Register Groups

Register Pointer

(FDh) High Nibble

Working Register

Group (Hex)

Actual Registers

(Hex)

1111b

F

F0–FF

1110b

E

E0–EF

1101b

D

D0–DF

1100b

C

C0–CF

1011b

B

B0–BF

1010b

A

A0–AF

1001b

9

90–9F

1000b

8

80–8F

0111b

7

70–7F

0110b

6

60–6F

0101b

5

50–5F

0100b

4

40–4F

0011b

3

30–3F

0010b

2

20–2F

0001b

1

10–1F

0000b

0

00–0F

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003