Power-on reset – Zilog Z86193 User Manual

Page 49

Z8

®

CPU

User Manual

UM001604-0108

Watchdog Timer

42

Bits 5, 6, and 7—These bits are reserved.

V

CC

Voltage Comparator—An on-board voltage comparator checks that V

CC

is at the

required level to insure correct operation of the device. Reset is globally driven if V

CC

is

below the specified voltage. This feature is available in select ROM Z8 devices. See the

device product specification for feature availability and operating range.

Power-On Reset

A timer circuit clocked by a dedicated on-board RC oscillator is used for the Power-On

Reset (POR) timer function, T

POR

. This POR time allows V

CC

and the oscillator circuit to

stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

•

Power fail to Power OK status (cold start)

•

Stop Mode Recovery (if bit 5 of SMR = 1)

•

WDT time-out

The POR time is specified as T

POR

. On Z8 devices that feature a Stop Mode Recovery

register (SMR), bit 5 selects whether the POR timer is used after Stop Mode Recovery or

by-passed. If bit D5 = 1 then the POR timer is used. If bit 5 = 0 then the POR timer is by-

passed. In this case, the Stop Mode Recovery source must be held in the recovery state for

5 T

P

C or 5 crystal clocks to pass the reset signal internally. This option is used when the

clock is provided with an RC/LC clock. See the device product specification for timing

details.

POR (cold start) always resets the Z8

®

CPU control and port registers to their default con-

dition. If a Z8 has a SMR, the warm start bit is reset to a 0 to indicate POR.

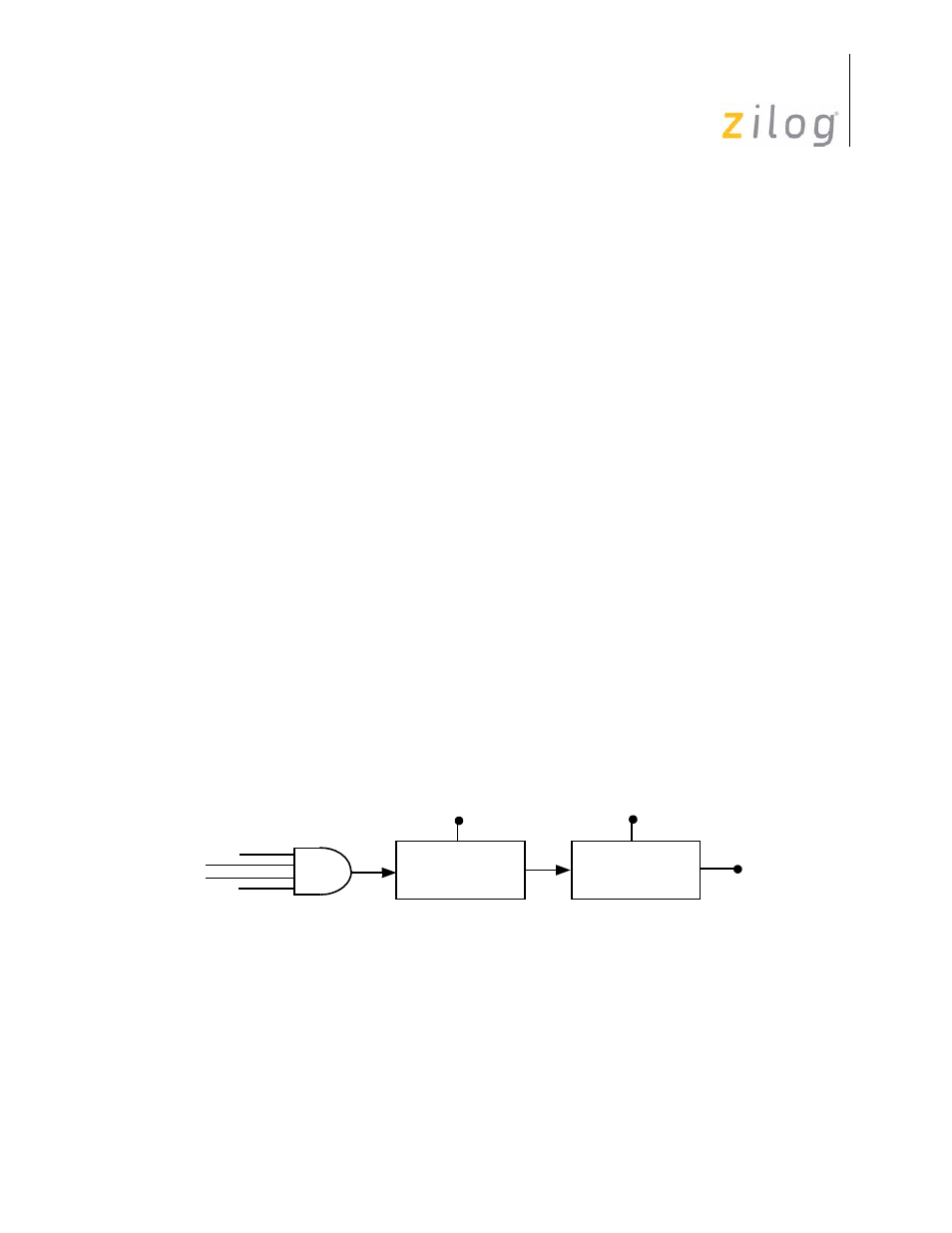

Figure 27. Example of Z8 with Simple SMR and POR

INT OSC

Chip

POR

Reset

P27

(Stop Mode)

(Cold Start)

VBO

WDT

Delay Line

T

POR

ms

18 CLK

Reset Filter

XTAL OSC

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003