Instruction timing, Figure 129 – Zilog Z86193 User Manual

Page 145

Z8

®

CPU

User Manual

UM001604-0108

External Interface

138

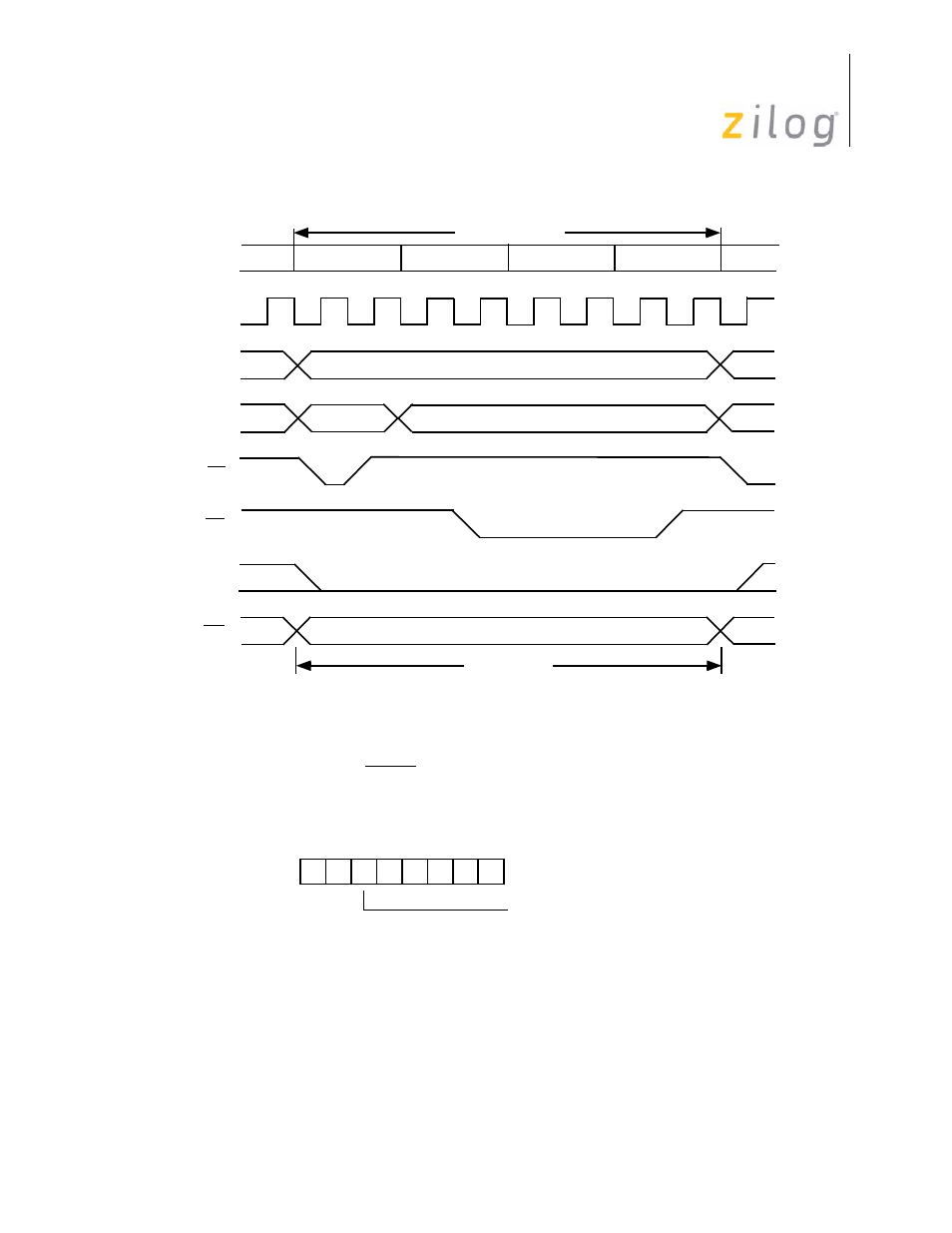

Timing is extended by setting bit D5 in the Port 0–1 Mode Register (

F8h

) to 1 (see

). After a RESET, this bit is set to 0.

Instruction Timing

The High throughput of Z8

®

CPU is due, in part, to the use of an instruction pipeline, in

which the instruction fetch and execution cycles are overlapped. During the execution of

Figure 129. Extended External Memory Write Cycle

Figure 130. Extended Bus Timing

Machine Cycle

T2

TX

T3

Clock

A15-A8

AD7–AD0

AS

DS

R/W

DM

Write Cycle

A15–A8

A7–A0

D7–D0 OUT

T1

D7 D6 D5 D4 D3 D2 D1 D0

(Write-Only)

Port 0–1 Register

Register F8h (P01M)

External Memory Timing

0 = Normal

1 = Extended

This manual is related to the following products:

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003