Interrupt request register (irq), displayed in, Figure 98 – Zilog Z86193 User Manual

Page 110

Z8

®

CPU

User Manual

UM001604-0108

Interrupts

103

IRQ is always cleared to

00h

and is read only until the first EI instruction, which enables

the IRQ to be read/written.

IMR is cleared before the IRQ enabling sequence to insure no unexpected interrupts occur

when EI is executed. This code sequence should be executed prior to programming the

application required values for IPR and IMR.

IRQ bits 6 and 7 are device dependent. When reserved, the bits are not used and return a 0

when read. When used as the Interrupt Edge select bits, the configuration options are as

listed in

EI

// Enable IRQ register, otherwise read only.

// Not required if interrupts were previously enabled.

DI

// Disable interrupt heading.

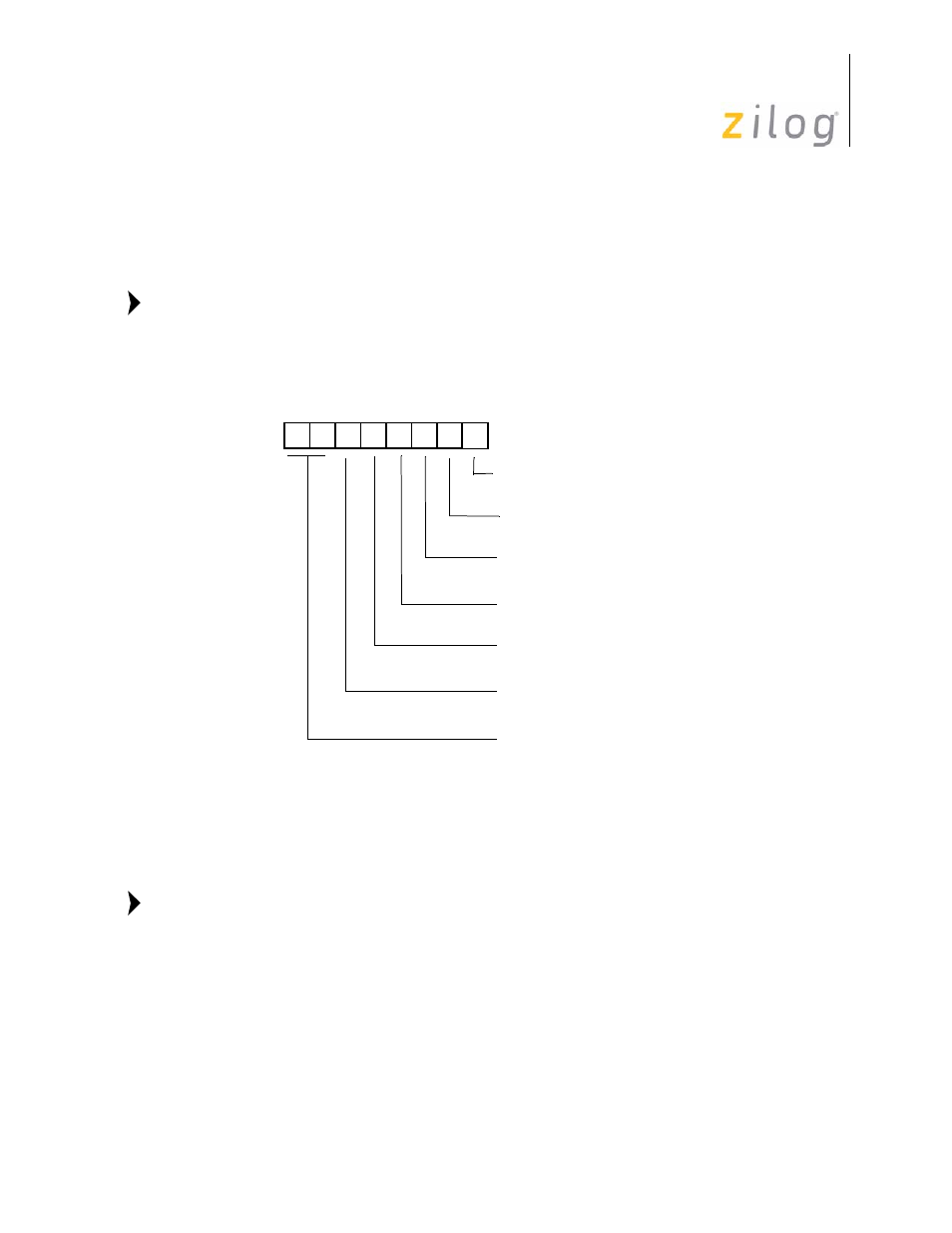

Figure 98. Interrupt Request Register

Note:

D7 D6 D5 D4 D3 D2 D1 D0

(Read/Write)

Reserved /Int Edge Select

Interrupt Request Register (IRQ)

Register FAh

0 = IRQ0 RESET

1 = IRQ0 SET

0 = IRQ1 RESET

1 = IRQ1 SET

0 = IRQ2 RESET

1 = IRQ2 SET

0 = IRQ3 RESET

1 = IRQ3 SET

0 = IRQ4 RESET

1 = IRQ4 SET

0 = IRQ5 RESET

1 = IRQ5 SET

Note:

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003