Zilog Z86193 User Manual

Page 165

Z8

®

CPU

User Manual

UM001604-0108

Instruction Description

158

Add

Syntax

ADD dst, src

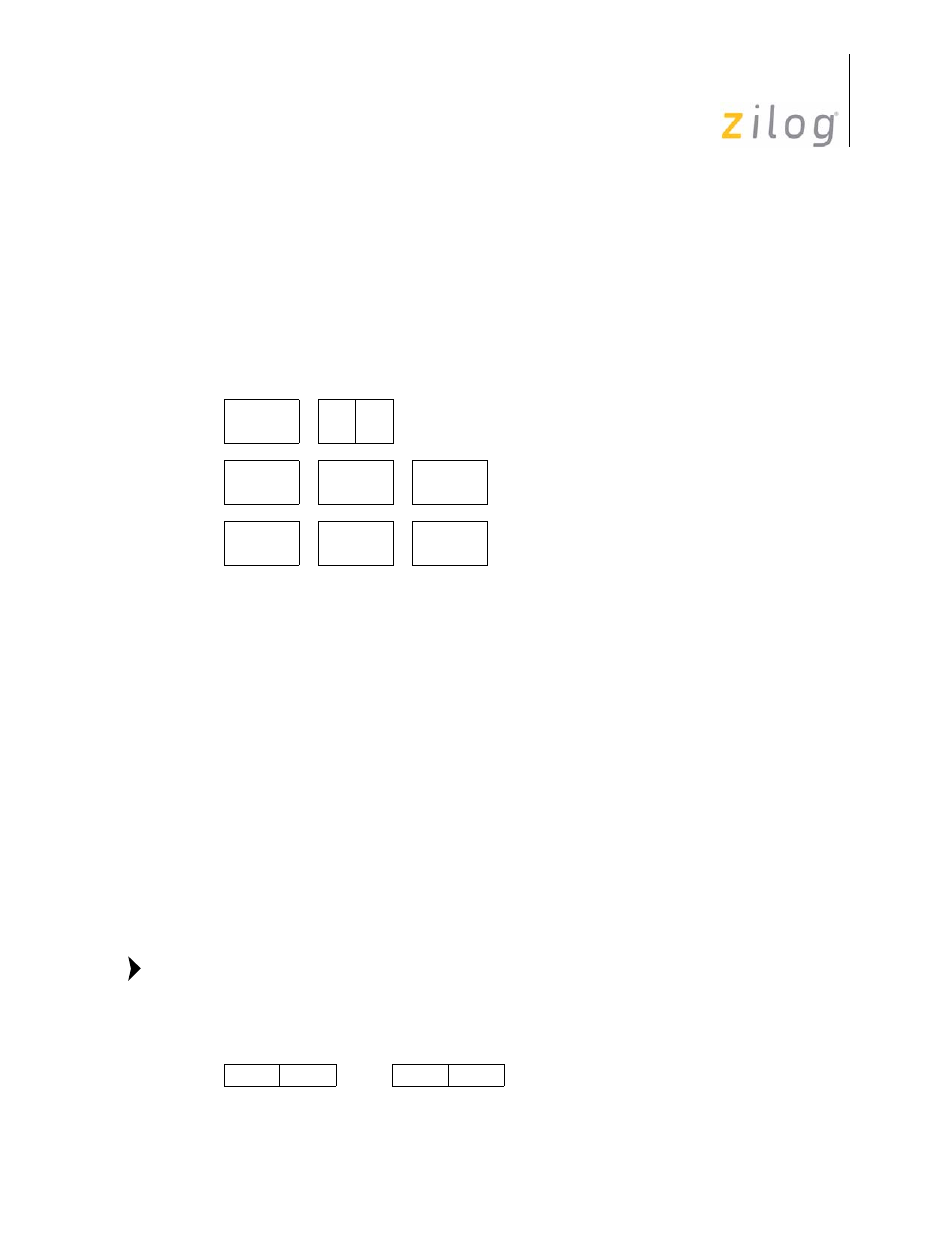

Instruction Format

Operation

dst

←

dst + src

The source operand is added to the destination operand. Two’s complement addition is

performed. The sum is stored in the destination operand. The contents of the source oper-

and are not affected.

Address modes R or IR can be used to specify a 4-bit Working Register. In this format, the

source or destination Working Register operand is specified by adding

1110b

(

Eh

) to the

high nibble of the operand. For example, if Working Register R12 (CH) is the destination

operand, then

ECh

is used as the destination operand in the Op Code.

Cycles

OPC (Hex)

Address Mode

dst

src

OPC

dst src

6

02

r

r

6

03

r

lr

OPC

src

dst

10

04

R

R

10

05

R

IR

OPC

dst

src

10

06

R

IM

10

07

IR

IM

Flags Description

C

Set if there is a carry from the most significant bit of the result;

cleared otherwise

Z

Set if the result is zero; cleared otherwise

S

Set if the result is negative; cleared otherwise

V

Set if an arithmetic overflow occurs, that is, if both operands are

of the same sign and the result is of the opposite sign; cleared

otherwise

D

Always cleared

H

Set if there is a carry from the most significant bit of the low order

four bits of the result; cleared otherwise

E

src

or

E

dst

Note:

- Z86233 Z86243 Z86733 Z86743 Z86C02 Z86C04 Z86C08 Z86C15 Z86C21 Z86C30 Z86C31 Z86C33 Z86C36 Z86C40 Z86C43 Z86C61 Z86C62 Z86C63 Z86C65 Z86C83 Z86C90 Z86C91 Z86C93 Z86C96 Z86E02 Z86E03 Z86E04 Z86E06 Z86E07 Z86E08 Z86E15 Z86E21 Z86E30 Z86E31 Z86E33 Z86E34 Z86E40 Z86E43 Z86E44 Z86E61 Z86E63 Z86E83 Z86K15 Z86L02 Z86L04 Z86L08 Z86L16 Z8E000 Z8E001 Z8PE003