Altera Stratix IV GX FPGA Development Board User Manual

Page 54

2–46

Chapter 2: Board Components

Components and Interfaces

Stratix IV GX FPGA Development Board

August 2012

Altera Corporation

Reference Manual

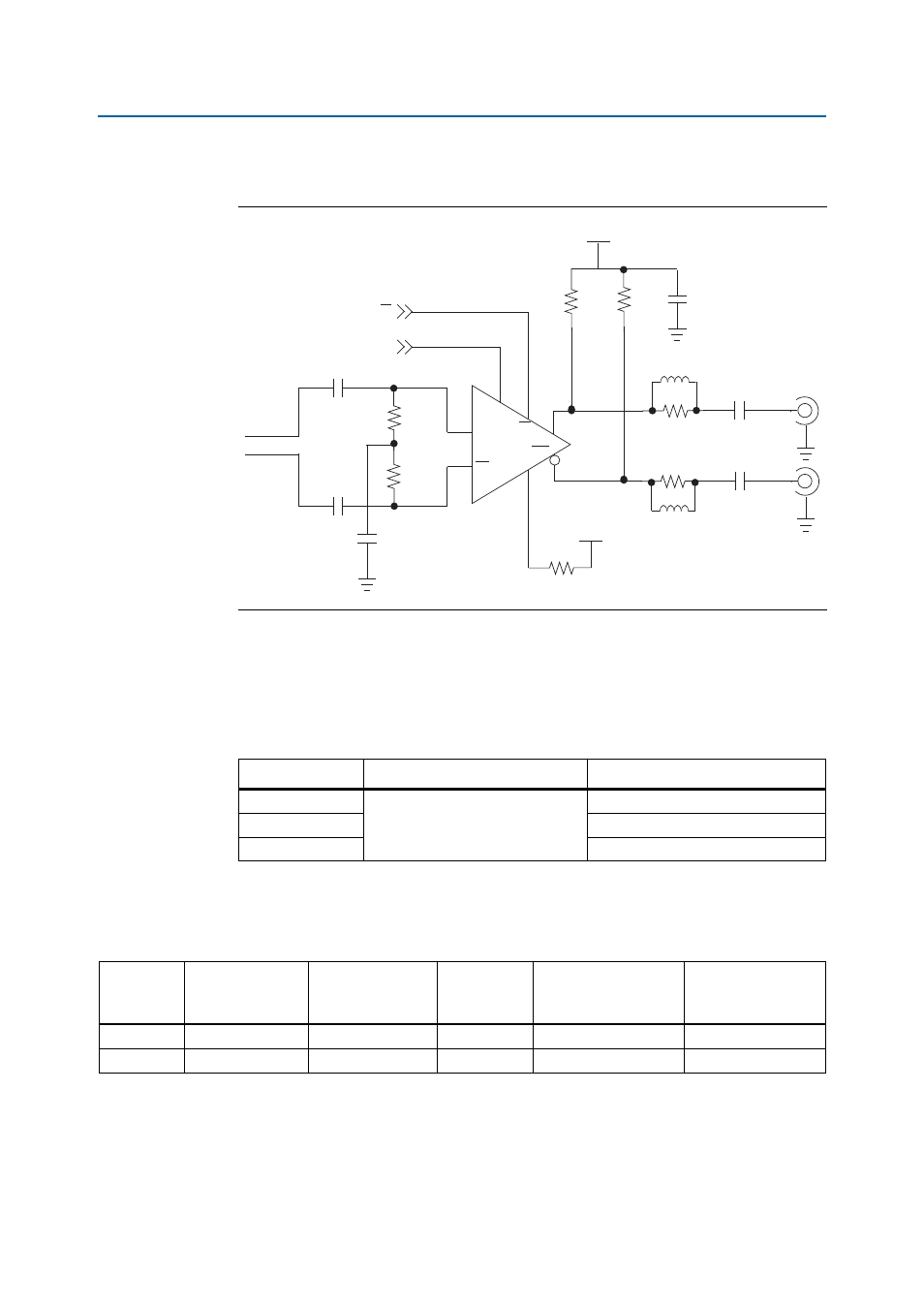

shows the SDI cable driver.

The LMH0344 cable equalizer supports operation at 270 Mbit SD, 1.5 Gbit HD, and

3.0 Gbit dual-link HD modes. Control signals are allowed for bypassing or disabling

the device, as well as a carrier detect or auto-mute signal interface.

lists the cable equalizer lengths.

lists the SDI video input interface pin assignments. The signal names and

directions are relative to the Stratix IV GX FPGA.

Figure 2–13. SDI Cable Driver

Table 2–44. SDI Cable Equalizer Lengths

Data Rate (Mbps)

Cable Type

Maximum Cable Length (m)

270

Belden 1694A

400

1485

140

2970

120

Differential

Input

V

cc

V

cc

ENABLE

LMH0302

1.0

μF

5.6 nH

75

Ω

75

Ω

750

Ω

75

Ω

75

Ω

49.9

Ω

49.9

Ω

1.0

μF

0.1

μF

0.1

μF

4.7

μF

4.7

μF

5.6 nH

SD/HD

SD/HD

SDO

SDO

ENABLE

SDI

SDI

R

REF

Table 2–45. SDI Video Input Interface Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 2)

Board

Reference

Description

Schematic

Signal Name

I/O Standard

MAX II CPLD EPM2210

System Controller

Pin Number

Stratix IV GX Device

Pin Number

U2.11

SDI video input P

SDI_RX_P

1.4-V PCML

—

L2

U2.10

SDI video input N

SDI_RX_N

1.4-V PCML

—

L1