Hdmi video output, Hdmi video output –42 – Altera Stratix IV GX FPGA Development Board User Manual

Page 50

2–42

Chapter 2: Board Components

Components and Interfaces

Stratix IV GX FPGA Development Board

August 2012

Altera Corporation

Reference Manual

lists the HSMC connector component reference and manufacturing

information.

HDMI Video Output

The Stratix IV GX FPGA development board includes a single HDMI video output

port based on the Analog Devices AD9889B HDMI transmitter device.

With the capability of up to 80 MHz operation, this device supports all video

resolutions from 480i to 1080i and UXGA at 60 Hz. This device also features a

programmable two-way color space converter which supports RGB, YCbCr, and

DDR, as well as ITU656-based embedded syncs and an automatic input video format

timing detection (CEA-861B) circuit.

On the digital audio aspect, this device supports standard S/PDIF for stereo LPCM or

compressed audio of up to 192 kHz. This device also supports 8-channel,

uncompressed, LPCM I2S audio of up to 192 kHz. No audio master clock is needed

for supporting S/PDIF and I2S.

This device supports an on-chip microcontroller (MCU) with I

2

C

®

master to perform

HDCP operations and EDID reading operations although the board does not have an

HDCP EEPROM installed by default. The on-chip MPU, accessible from the FPGA

through the serial port, reports HDMI events through interrupts and registers.

J2.149

LVDS TX bit 16 or CMOS bit 72

HSMB_TX_D_P16

LVDS or 2.5-V

R13

J2.150

LVDS RX bit 16 or CMOS bit 73

HSMB_RX_D_P16

LVDS or 2.5-V

F10

J2.151

LVDS TX bit 16n or CMOS bit 74

HSMB_TX_D_N16

LVDS or 2.5-V

P13

J2.152

LVDS RX bit 16n or CMOS bit 75

HSMB_RX_D_N16

LVDS or 2.5-V

E10

J2.155

LVDS or CMOS clock out 2 or CMOS bit 76

HSMB_CLK_OUT_P2

LVDS or 2.5-V

K10

J2.156

LVDS or CMOS clock in 2 or CMOS bit 77

HSMB_CLK_IN_P2

LVDS or 2.5-V

W6

J2.157

LVDS or CMOS clock out 2 or CMOS bit 78

HSMB_CLK_OUT_N2

LVDS or 2.5-V

J10

J2.158

LVDS or CMOS clock in 2 or CMOS bit 79

HSMB_CLK_IN_N2

LVDS or 2.5-V

W5

J2.160

HSMC Port B presence detect

HSMB_PRSNTn

2.5-V

D9

D15

User LED to show RX data activity on

HSMC Port B

HSMB_RX_LED

2.5-V

AT10

D14

User LED to show TX data activity on HSMC

Port B

HSMB_TX_LED

2.5-V

AH33

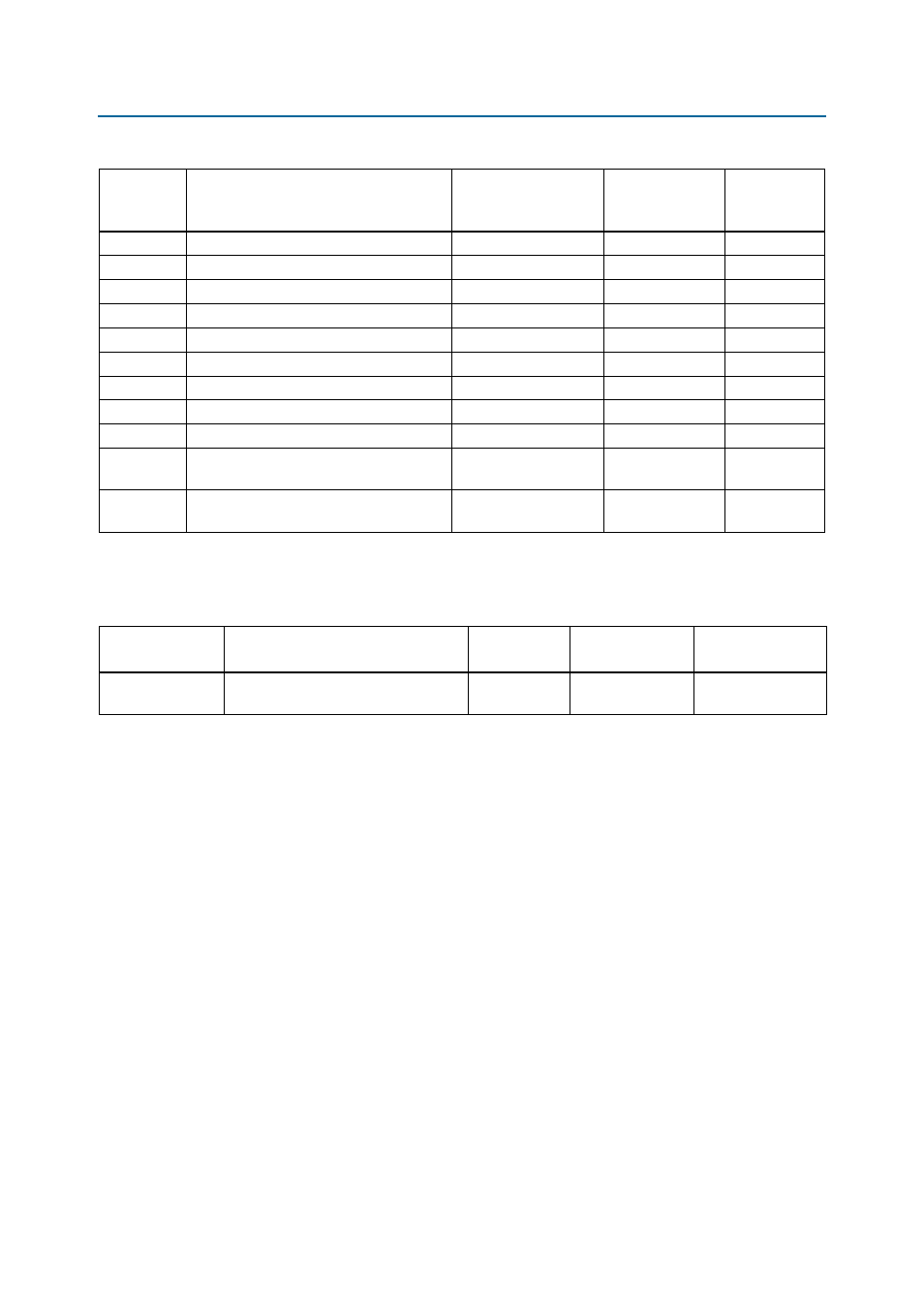

Table 2–38. HSMC Port B Pin Assignments, Schematic Signal Names, and Functions (Part 4 of 4)

Board

Reference

Description

Schematic Signal

Name

I/O Standard

Stratix IV GX

Device

Pin Number

Table 2–39. HSMC Connector Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

J1 and J2

HSMC, custom version of QSH-DP

family high-speed socket.

Samtec

ASP-122953-01