Altera Arria V GT FPGA Development Board User Manual

Page 42

2–32

Chapter 2: Board Components

General User Input/Output

Arria V GT FPGA Development Board

December 2014

Altera Corporation

Reference Manual

Table 2–21

summarizes the SDI video output interface pin assignments, signal names,

and functions.

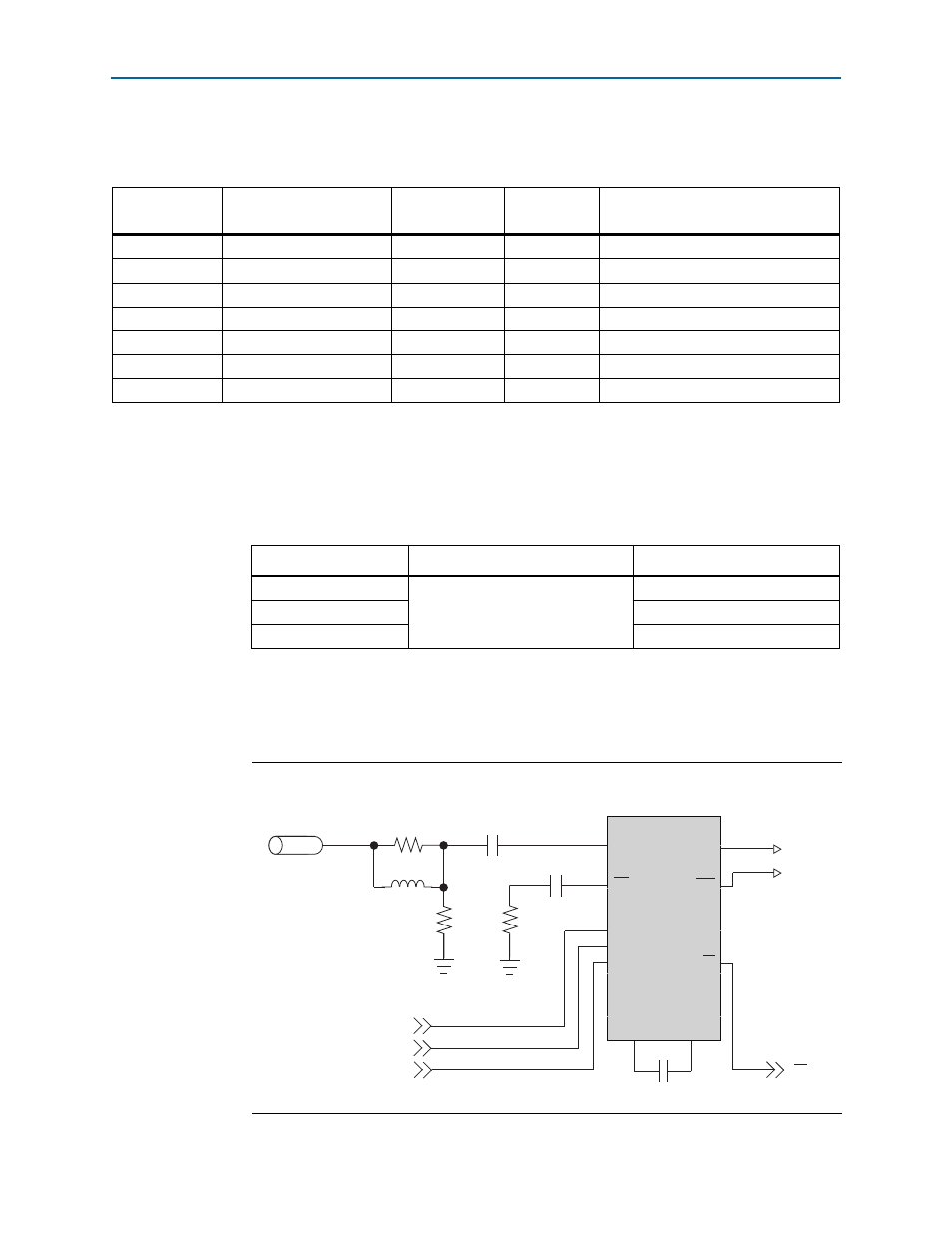

The cable equalizer supports operation at 270 Mbit SD, 1.5 Gbit HD, and 3.0 Gbit

dual-link HD modes. Control signals are allowed for bypassing or disabling the

device, as well as a carrier detect or auto-mute signal interface.

Table 2–22

lists the cable equalizer lengths.

Figure 2–7

is an excerpt from the LMH0384SQ cable equalizer data sheet that shows

the SDI cable equalizer. On this development board, the output is a single-ended

output, with the negative channel driving a load local to the board.

Table 2–21. SDI Video Output Interface Pin Assignments, Schematic Signal Names, and Functions

Board

Reference (U24)

Schematic

Signal Name

Arria V GT FPGA

Pin Number

I/O Standard

Description

1

SDI_A_TX_P

AH3

1.4-V PCML

SDI video input P

2

SDI_A_TX_N

AH4

1.4-V PCML

SDI video input N

4

SDI_A_TX_RSET

—

3.3-V

Device reset pull up register

6

SDI_A_TX_EN

AK31

2.5-V

Device enable

10

SDI_A_TX_SD_HDN

M20

2.5-V

High definition select

11

SDI_A_TXDRV_N

—

3.3-V

SDI video output from cable driver N

12

SDI_A_TXDRV_P

—

3.3-V

SDI video output from cable driver P

Table 2–22. SDI Cable Equalizer Lengths

Data Rate (Mbps)

Cable Type

Maximum Cable Length (m)

270

Belden 1694A

400

1485

140

2970

120

Figure 2–7. SDI Cable Equalizer

BYPASS

MUTE

REF

1.0

μF

75

Ω

37.4

Ω

1.0

μF

1.0

μF

CD

SDI

SDI

SDO

SDO

CD

MUTE

MUTE

REF

BYPASS

AEC+

AEC–

75

Ω

MUTE

Coaxial Cable

SDI Adaptive

Cable Equalizer

To FPGA

3.9 nH