Altera Arria V GT FPGA Development Board User Manual

Page 36

2–26

Chapter 2: Board Components

Clock Circuitry

Arria V GT FPGA Development Board

December 2014

Altera Corporation

Reference Manual

Table 2–13

lists the clock outputs for the development board.

HSMC

HSMB_CLK_IN_P2

LVDS/LVTTL

AU32

LVDS input from the installed HSMC cable or

board. Can also support 2x LVTTL inputs.

HSMB_CLK_IN_N2

LVDS/LVTTL

AT32

PCI Express

Edge

PCIE_REFCLK_P

LVDS/LVTTL

AG32

LVDS input from the PCI Express edge connector.

PCIE_REFCLK_N

HCSL

AG33

FMC

FMC_REFCLK_P0

LVDS

AB9

LVDS input from the FMC board (drives two

REFCLKs on FPGA 2)

FMC_REFCLK_P1

LVDS

V9

FMC_REFCLK_N0

LVDS

AB8

FMC_REFCLK_N1

LVDS

V8

FMC_CLK_M2C_P0

LVDS

AV19

LVDS input from the FMC board.

FMC_CLK_M2C_P1

LVDS

AF21

FMC_CLK_M2C_N0

LVDS

AU19

FMC_CLK_M2C_N0

LVDS

AE21

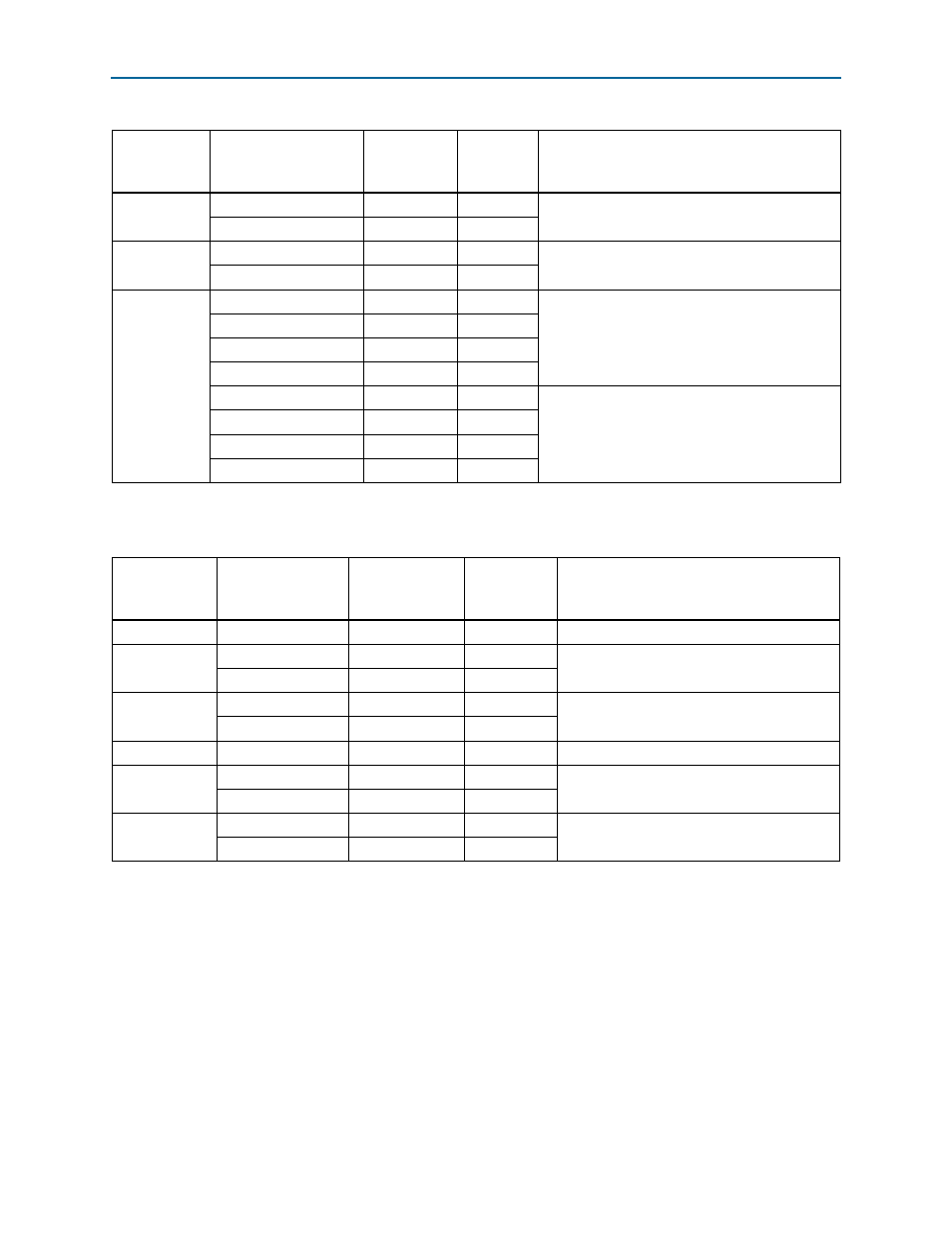

Table 2–12. Off-Board Clock Inputs

Source

Schematic Signal

Name

I/O Standard

Arria V GT

FPGA Pin

Number

Description

Table 2–13. Off-Board Clock Outputs

Source

Schematic Signal

Name

I/O Standard

Arria V GT

FPGA Pin

Number

Description

HSMC

HSMA_CLK_OUT0

2.5V CMOS

AL14

FPGA CMOS output (or GPIO)

HSMC

HSMA_CLK_OUT_P1

LVDS/2.5V CMOS

AU13

LVDS output. Can also support 2x CMOS

outputs.

HSMA_CLK_OUT_N1

LVDS/2.5V CMOS

AT13

HSMC

HSMA_CLK_OUT_P2

LVDS/2.5V CMOS

AM7

LVDS output. Can also support 2x CMOS

outputs.

HSMA_CLK_OUT_N2

LVDS/2.5V CMOS

AL7

HSMC

HSMB_CLK_OUT0

2.5V CMOS

AJ33

FPGA CMOS output (or GPIO)

HSMC

HSMB_CLK_OUT_P1

LVDS/2.5V CMOS

AM33

LVDS output. Can also support 2x CMOS

outputs.

HSMB_CLK_OUT_N1

LVDS/2.5V CMOS

AL34

HSMC

HSMB_CLK_OUT_P2

LVDS/2.5V CMOS

AU32

LVDS output. Can also support 2x CMOS

outputs.

HSMB_CLK_OUT_N2

LVDS/2.5V CMOS

AD26