Altera Arria V GT FPGA Development Board User Manual

Page 33

Chapter 2: Board Components

2–23

Clock Circuitry

December 2014

Altera Corporation

Arria V GT FPGA Development Board

Reference Manual

shows the default frequencies of all external clocks going to the Arria V GT

FPGA development board.

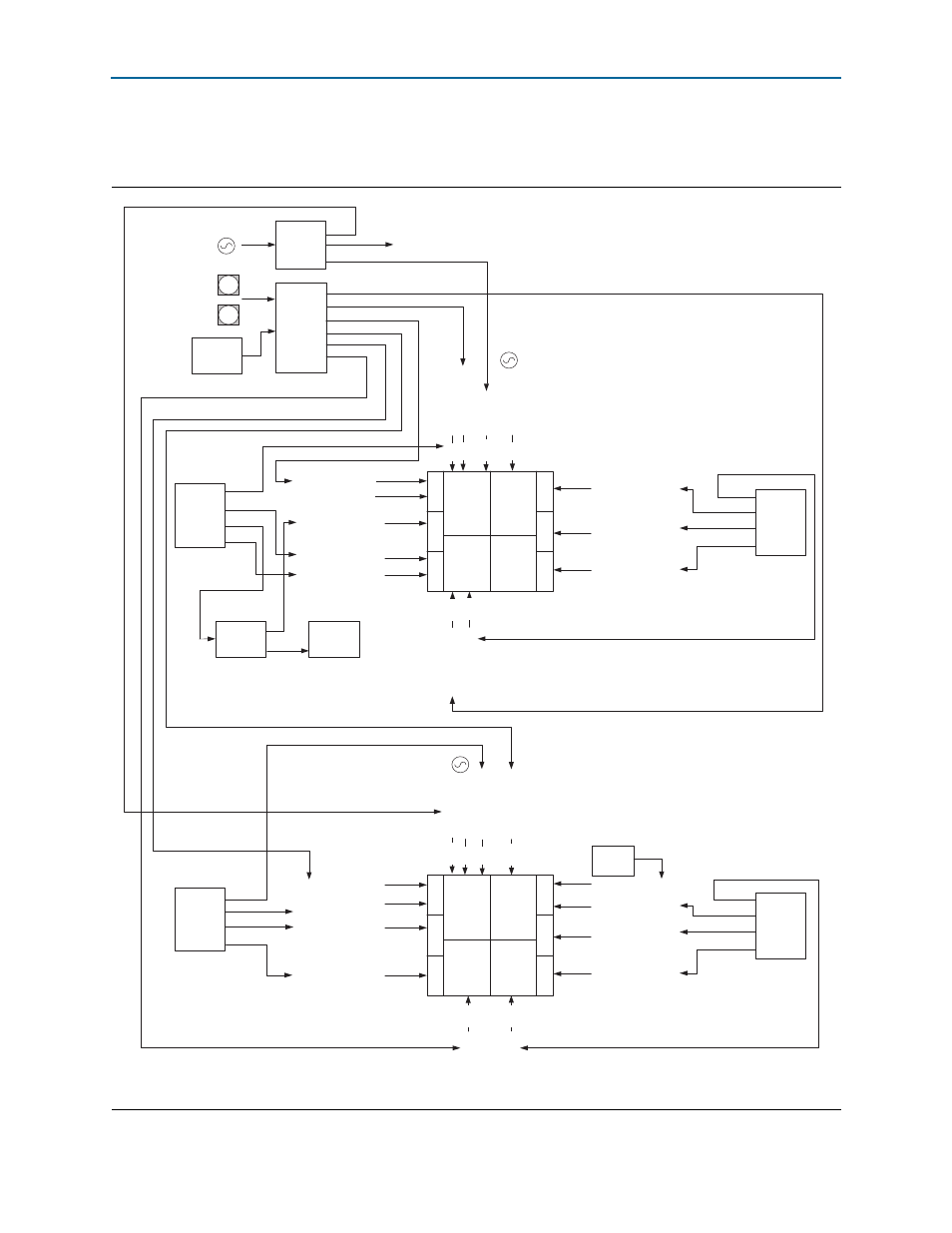

Figure 2–6. Arria V GT FPGA Development Board Clocks

r

(

p

R

SMA

SMA

50 MHz

50 MHz

50 MHz

50 MHz

100 MHz

100 MHz

100 MHz

100 MHz

100 MHz

50 MHz

100 MHz

100 MHz

100 MHz

100 MHz

125 MHz

125 MHz

125 MHz

625 MHz

156.25 MHz

156.25 MHz

125 MHz

125 MHz

125 MHz

625 MHz

125 MHz

125 MHz

125 MHz

625 MHz

625 MHz

125 MHz

125 MHz

156.25 MHz

125 MHz

125 MHz

148.5 MHz

Default

100 MHz

Default

100 MHz

Default

B u ffe

S i5 7 0

RE

F

C

L

K

IN

P

U

T

B u ffe r

C L K IN _ M A X _ 5 0

X7

U56

U51

X6

P C IE _ R E F _ C L K _ P /N

R E F C L K 1 A _ Q L 0 _ P /N

(P C Ie )

R E F C L K 3 _ A _ Q L 1 _ P /N

(S F P + )

CL

K

6

C

L

KI

N

B

O

T

A_

P/

N

[0

]

CL

K

IN

B

O

T

A

_

P

/N

[1

]

CL

K

7

R E F C L K 2 _ A _ Q L 1 _ P /N

(S F P + )

R E F C L K 4 _ A _ Q L 2 _ P /N

(S F P + )

C

L

KA_

1

2

5

_

P

/N

CL

K

0

CL

K

INA

_

5

0

CL

K

5

U16

U53

S i5 3 8 8

CLK0

CLK1

CLK2

CLK3

CL

K

1

7

CL

K

1

9

CL

K

INT

O

P

A

_

P

/N[

0

]

CL

K

INT

O

P

A

_

P

/N[

1

]

J16

U25

Bullseye

Connector

Clock Buffer

1:2

B 8

B 7

B 3

B 4

QL 2

QL 1

QL 0

QR2

QR1

QR0

R E F C L K 2 _ A _ Q R 1 _ P /N

(C 2 C , H S M A )

R E F C L K 0 _ A _ Q R 0 _ P /N

C 2 C )

R E F C L K 4 _ A _ Q R 2 _ P /N

H S M A )

U48

S i5 3 8 8

CLK0

CLK1

CLK2

CLK3

CL

K

11

CL

K

IN

B

O

T

B

_P

/N

[0]

CL

K

INB

O

T

B

_

P

/N[

1

]

CL

K

7

CL

K

B

_125_P

/N

CL

K

6

C

LK

IN

B

_50

CL

K

0p

S i5 7 1

U53

U13

R E F C L K 1 _ B _ Q L 0 _ P /N

R E F C L K 2 _ B _ Q L 1 _ P /N

(C 2 C )

C

LK

15

CL

K

20

C

L

KI

N

T

O

P

B

_

P

/N

[0

]

C

L

KI

N

T

O

P

B

_

P

/N

[1

]

S i5 3 8 8

R E F C L K 0 _ B _ Q L 0 _ P /N

(C 2 C )

CLK0

CLK1

CLK2

CLK3

R E F C L K 4 _ B _ Q L 2 _ P /N

(C 2 C )

U34

R E F C L K 2 _ B _ Q R 1 _ P /N

(F M C )

R E F C L K 1 _ B _ Q R 0 _ P /N

(H S M B , S D I)

R E F C L K 3 _ B _ Q R 2 _ P /N

(F M C )

B 8

B 7

B 3

B 4

QL 2

QL 1

QL 0

QR2

QR1

QR0

E F C L K 0 _ B _ Q R 0 _ P /N

(H S M B , S D I)

U52

S i5 3 8 8

CLK0

CLK1

CLK2

CLK3

SDI (148.5 M/148.35 M)

(