10/100/1000 ethernet, 10/100/1000 ethernet –26 – Altera Cyclone V GT FPGA Development Board User Manual

Page 34

2–26

Chapter 2: Board Components

Components and Interfaces

Cyclone V GT FPGA Development Board

September 2014

Altera Corporation

Reference Manual

10/100/1000 Ethernet

The development board supports 10/100/1000 base-T Ethernet using an external

Marvell 88E1111 PHY and Altera Triple-Speed Ethernet MegaCore MAC function. The

PHY-to-MAC interface employs a RGMII interface. The MAC function must be

provided in the FPGA for typical networking applications.

The Marvell 88E1111 PHY uses 2.5-V and 1.0-V power rails and requires a 25-MHz

reference clock driven from a dedicated oscillator. The PHY interfaces to a RJ45 model

with internal magnetics for driving copper lines with Ethernet traffic.

shows the RGMII interface between the FPGA (MAC) and Marvell 88E1111

PHY.

lists the Ethernet PHY interface pin assignments.

B28

PCIE_RX_N3

AC1

1.5-V PCML

Receive bus

B5

PCIE_SMBCLK

AP5

LVTTL

SMB clock

B6

PCIE_SMBDAT

AJ12

LVTTL

SMB data

A16

PCIE_TX_P0

AH4

1.5-V PCML

Transmit bus

A17

PCIE_TX_N0

AH3

1.5-V PCML

Transmit bus

A21

PCIE_TX_P1

AF4

1.5-V PCML

Transmit bus

A22

PCIE_TX_N1

AF3

1.5-V PCML

Transmit bus

A25

PCIE_TX_P2

AD4

1.5-V PCML

Transmit bus

A26

PCIE_TX_N2

AD3

1.5-V PCML

Transmit bus

A29

PCIE_TX_P3

AB4

1.5-V PCML

Transmit bus

A30

PCIE_TX_N3

AB3

1.5-V PCML

Transmit bus

B11

PCIE_WAKEn

AP6

LVTTL

Wake signal

Table 2–20. PCI Express Pin Assignments, Schematic Signal Names, and Functions (Part 2 of 2)

Board

Reference (J16)

Schematic Signal Name

Cyclone V GT

Pin Number

I/O Standard

Description

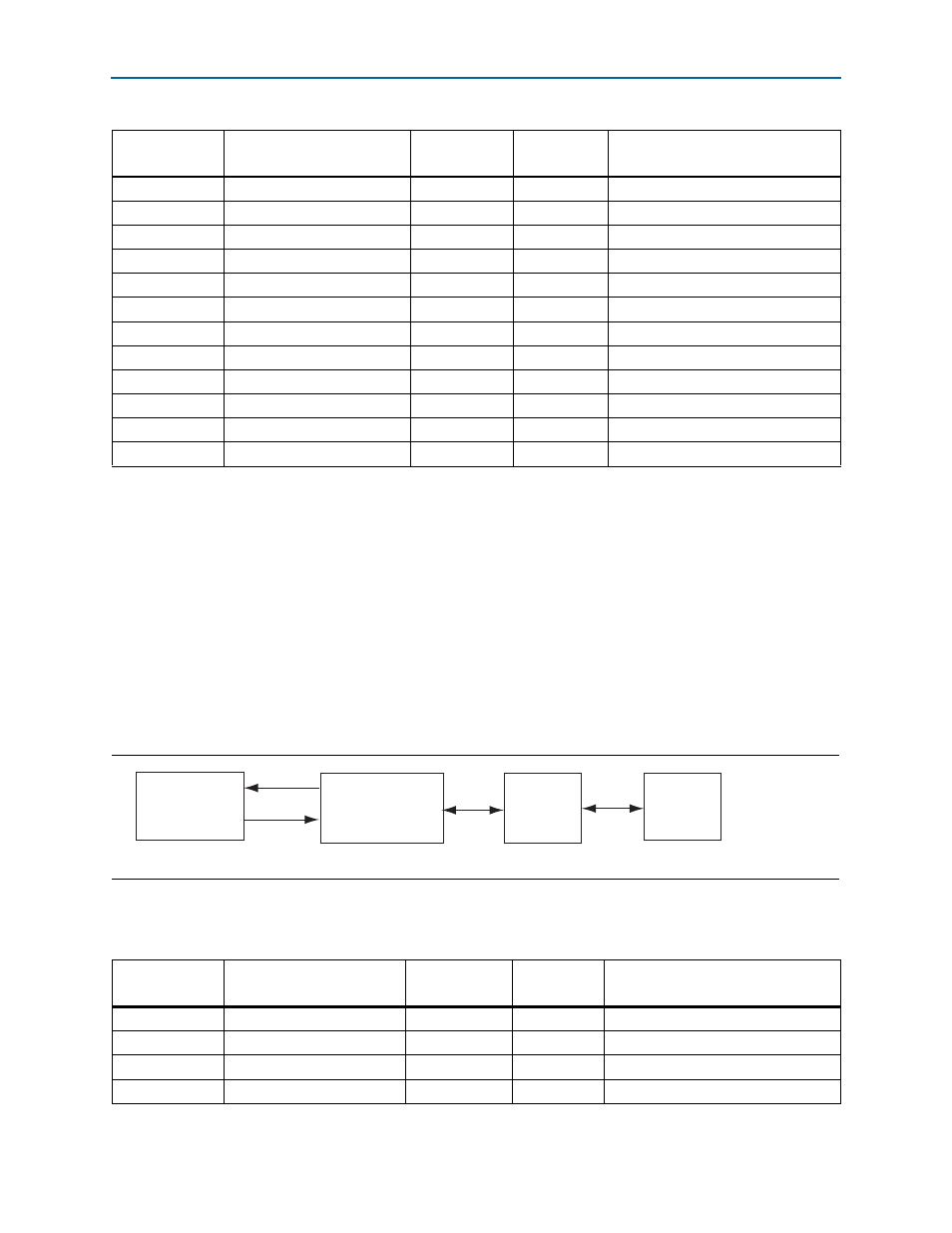

Figure 2–7. RGMII Interface between FPGA (MAC) and Marvell 88E1111 PHY

10/100/1000 Mbps

Ethernet MAC

Marvell 88E1111

PHY

Device

Transformer

RJ45

RGMII Interface

TXD[3:0]

RXD[3:0]

CAT 5 UTP:

- 10BASE-T

- 100BASE-TX

- 1000BASE-T

Table 2–21. Ethernet PHY Pin Assignments, Signal Names and Functions (Part 1 of 2)

Board

Reference (U11)

Schematic Signal Name

Cyclone V GT

Pin Number

I/O Standard

Description

8

ENET_GTX_CLK

AP7

2.5-V CMOS

125-MHz RGMII transmit clock

23

ENET_INTN

AK10

2.5-V CMOS

Management bus interrupt

60

ENET_LED_DUPLEX

—

2.5-V CMOS

Duplex or collision LED. Not used

70

ENET_LED_DUPLEX

—

2.5-V CMOS

Duplex or collision LED. Not used