Altera Cyclone V GT FPGA Development Board User Manual

Page 15

Chapter 2: Board Components

2–7

MAX V CPLD 5M2210 System Controller

September 2014

Altera Corporation

Cyclone V GT FPGA Development Board

Reference Manual

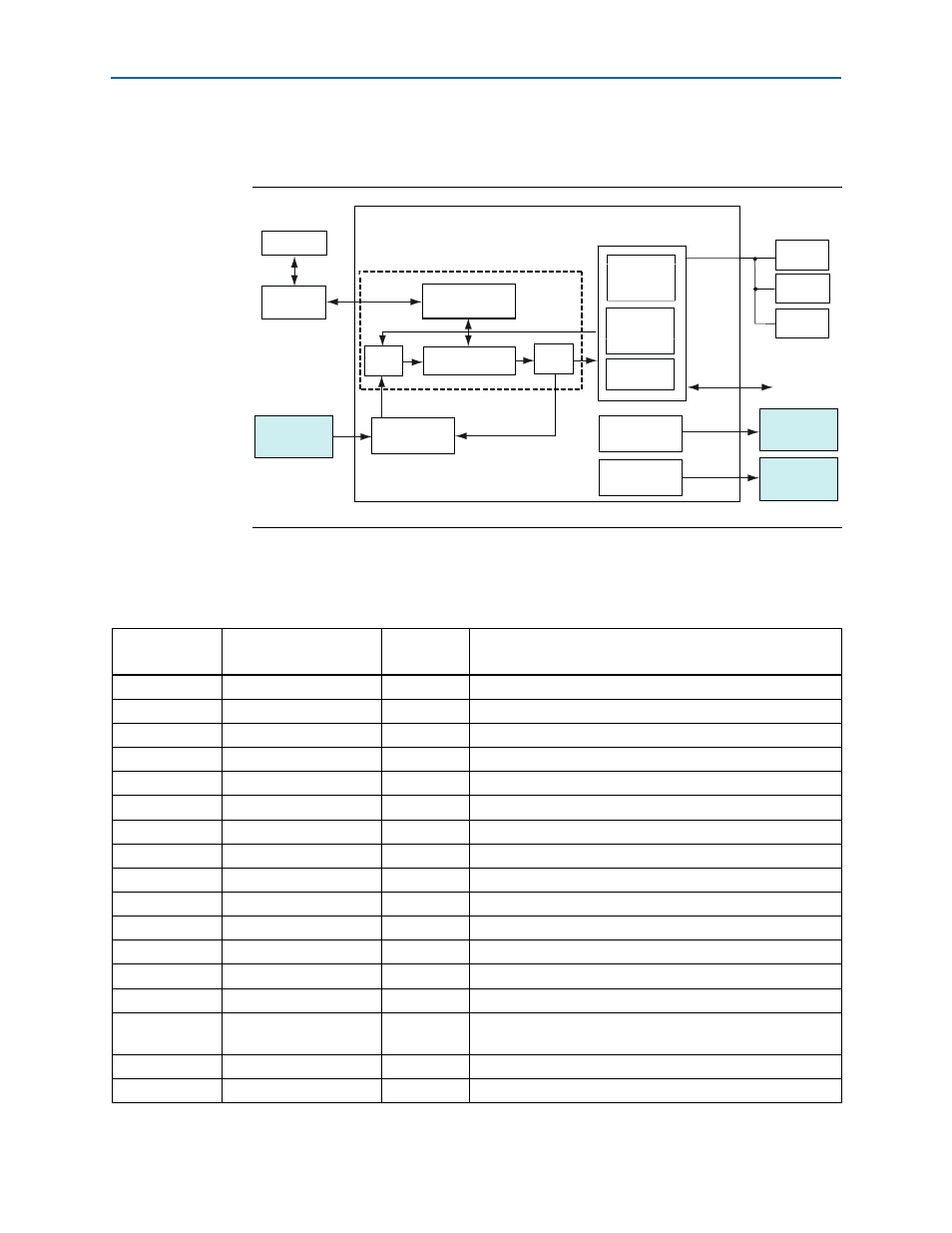

illustrates the MAX V CPLD 5M2210 System Controller's functionality and

external circuit connections as a block diagram.

lists the I/O signals present on the MAX V CPLD 5M2210 System

Controller. The signal names and functions are relative to the MAX V device.

Figure 2–2. MAX V CPLD 5M2210 System Controller Block Diagram

Information

Register

Embedded

USB-Blaster II

Si571

Controller

Si570

Controller

SLD-HUB

PFL

FSM Bus

MAX V CPLD System Controller

Power

Measurement

Results

Virtual-JTAG

PC

FPGA

LTC2418

Controller

Flash

Decoder

Encoder

GPIO

JTAG Control

SSRAM

Control

Register

Si571

Programmable

Oscillator

Si570

Programmable

Oscillator

Table 2–5. MAX V CPLD 5M2210 System Controller Device Pin-Out (Part 1 of 5)

Board

Reference (U32)

Schematic Signal Name

I/O Standard

Description

L2

ASSP_CPLD_MRN

2.5-V

For ASSP design (optional)

R12

ASSP_MODE

2.5-V

For ASSP design (optional)

B9

CLK125_EN

2.5-V

125 MHz oscillator enable

E9

CLK50_EN

2.5-V

50 MHz oscillator enable

J5

CLK_CONFIG

2.5-V

100 MHz configuration clock input

A15

CLK_ENABLE

2.5-V

DIP switch for clock oscillator enable

A13

CLK_SEL

2.5-V

DIP switch for clock select—SMA or oscillator

J12

CLKIN_MAX_50

2.5-V

50 MHz clock input

C9

CLOCK_SCL

2.5-V

Programmable oscillator I

2

C clock

D9

CLOCK_SDA

2.5-V

Programmable oscillator I

2

C data

D10

CPU_RESETN

2.5-V

FPGA reset push button

M1

EXTRA_SIG0

2.5-V

Embedded USB-Blaster II interface. Reserved for future use

T13

EXTRA_SIG1

1.8-V

Embedded USB-Blaster II interface. Reserved for future use

T15

EXTRA_SIG2

1.8-V

Embedded USB-Blaster II interface. Reserved for future use

R14

FACTORY_REQUEST

1.8-V

Embedded USB-Blaster II request to send FACTORY

command

N12

FACTORY_STATUS

1.8-V

Embedded USB-Blaster II FACTORY command status

A2

FACTORY_USER

1.8-V

DIP switch to load factory or user design at power-up