Fpga configuration mode dip switch, Cpu reset push button – Altera Cyclone V GT FPGA Development Board User Manual

Page 25

Chapter 2: Board Components

2–17

Setup Elements

September 2014

Altera Corporation

Cyclone V GT FPGA Development Board

Reference Manual

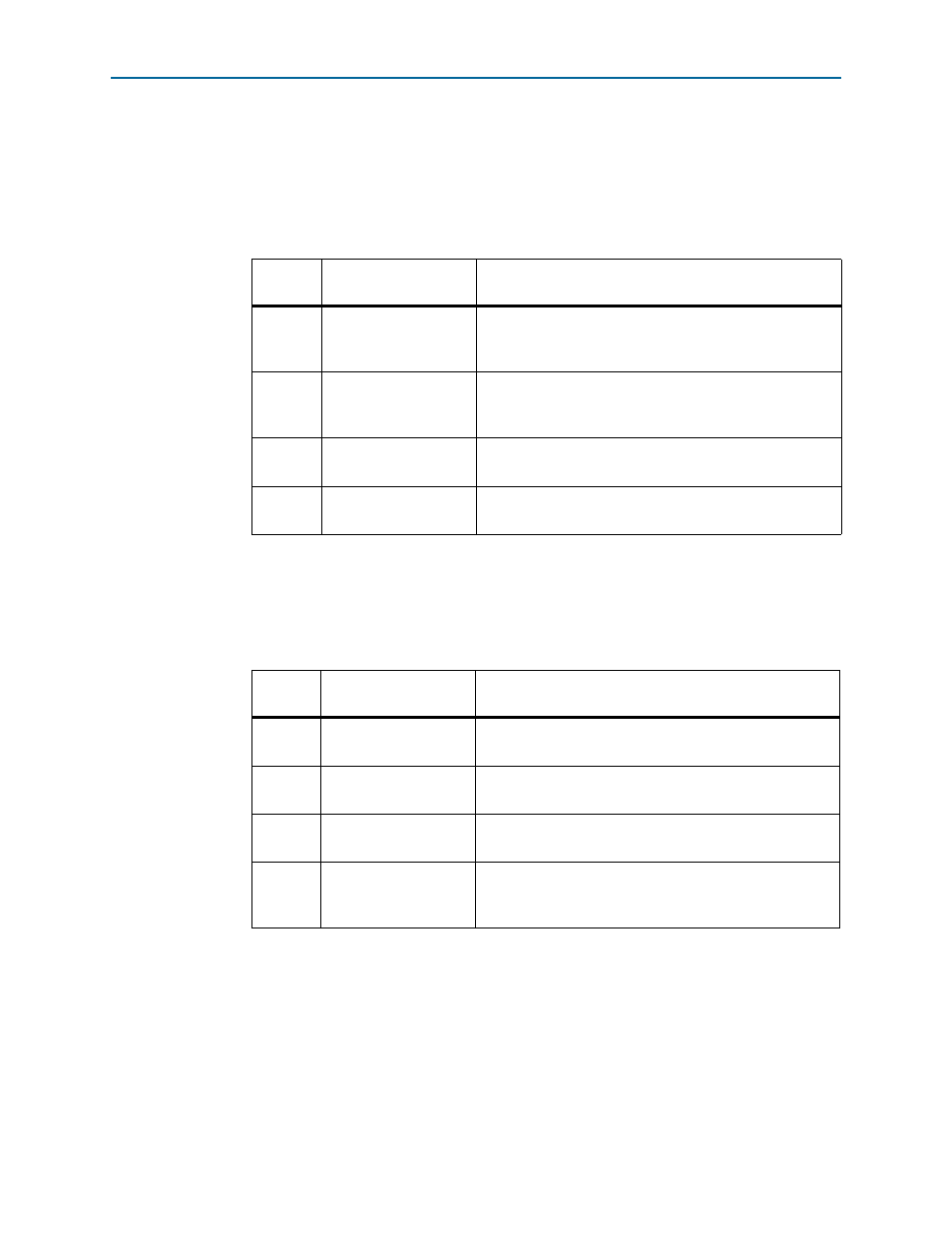

JTAG Chain Control or PCI Express Control DIP Switch

The JTAG chain control DIP switch (SW3) either remove or include devices in the

active JTAG chain. The Cyclone V GT FPGA is always in the JTAG chain. This switch

also enables or disables different link width configurations for the PCI Express

connector.

lists the switch controls and its descriptions.

FPGA Configuration Mode DIP Switch

The FPGA configuration mode DIP switch (SW5) defines the mode to use to configure

the FPGA.

lists the switch controls and its descriptions.

CPU Reset Push Button

The CPU reset push button,

CPU_RESETn

(S4), is an input to the Cyclone V GT DEV_CLRn

pin and is an open-drain I/O from the MAX V CPLD System Controller. This push

button is the default reset for both the FPGA and CPLD logic. The MAX V CPLD

5M2210 System Controller also drives this push button during power-on-reset (POR).

Table 2–9. JTAG Chain Control DIP Switch

Switch

Position

Schematic Signal Name

Description

1

PCIe_PRSNT2n_X1

ON: Bypass PCI Express edge connector

OFF: PCI Express edge connector in-chain and enable x1

presence detect

2

PCIe_PRSNT2n_X4

ON: Bypass PCI Express edge connector

OFF: PCI Express edge connector in-chain and enable x4

presence detect

3

HSMB_JTAG_EN

ON: Bypass HSMC port B

OFF: HSMC port B in-chain

4

HSMA_JTAG_EN

ON: Bypass HSMC port A

OFF: HSMC port A in-chain

Table 2–10. FPGA Configuration Mode DIP Switch

Switch

Position

Schematic Signal Name

Description

1

FPGA_MSEL1

ON: Select logic 0

OFF: Select logic 1

2

FPGA_MSEL2

ON: Select logic 0

OFF: Select logic 1

3

FPGA_MSEL4

ON: Select logic 0

OFF: Select logic 1

4

FORCE_FAN

Optional fan control function to add into the MAX V CPLD

System Controller.

Not used by default.