Altera Cyclone V GT FPGA Development Board User Manual

Page 12

2–4

Chapter 2: Board Components

Board Overview

Cyclone V GT FPGA Development Board

September 2014

Altera Corporation

Reference Manual

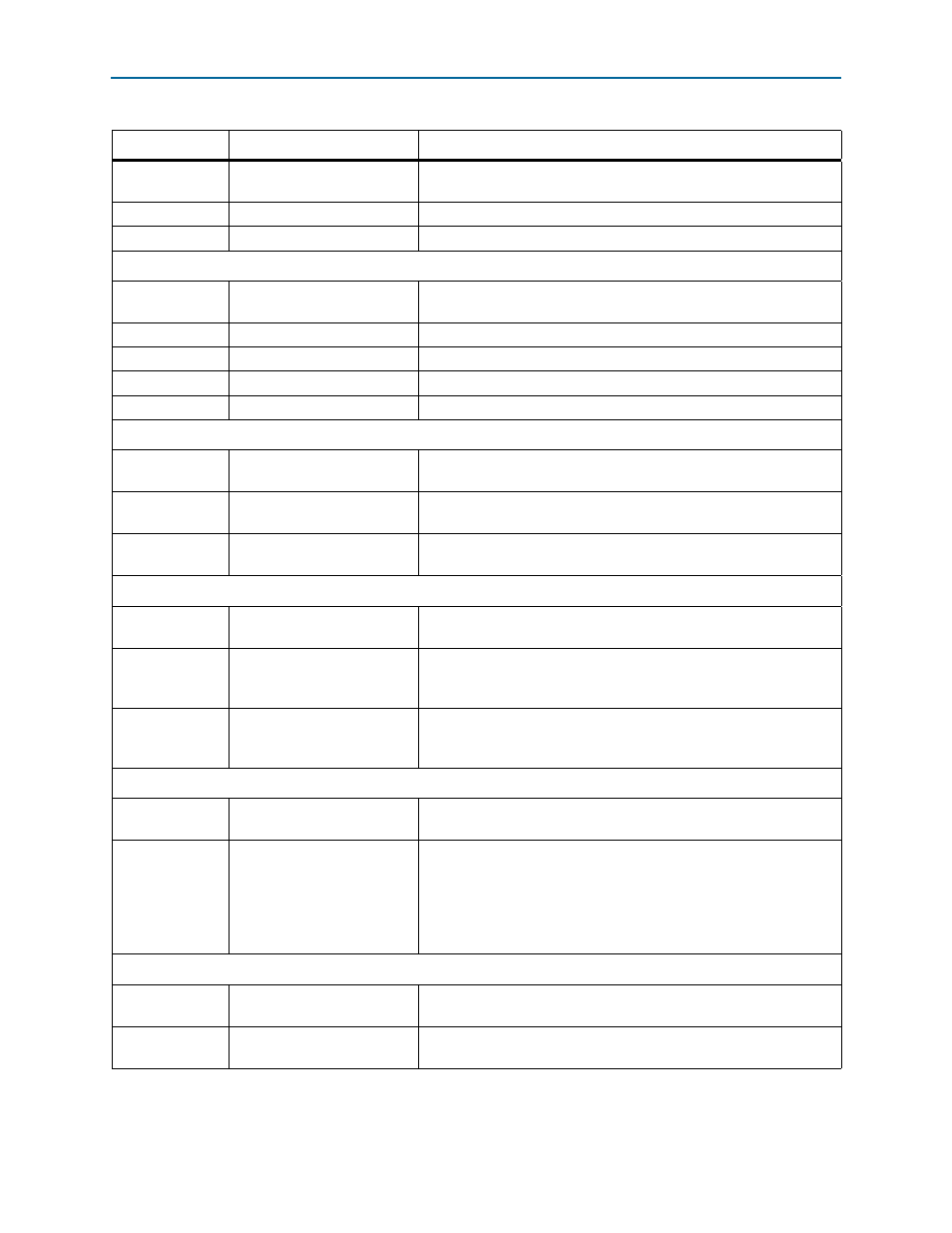

J3, J6

Clock input SMA connectors

Drive LVPECL-compatible clock inputs into the clock multiplexer

buffer.

J4, J7

Clock output SMA connectors

Drives out 2.5-V CMOS clock output from the clock buffer (U3).

J14

SMA connector

SMA to or from the FPGA, which can be an I/O or a clock output.

General User Input/Output

D8–D11,

D15–D18

User LEDs

Eight user LEDs. Illuminates when driven low.

SW1

User DIP switch

Quad user DIP switches. When the switch is ON, a logic 0 is selected.

S4

CPU reset push button

Reset the FPGA logic.

S7

MAX V reset push button

Reset the MAX V CPLD 5M2210 System Controller.

S1–S3

General user push buttons

Three user push buttons. Driven low when pressed.

Memory Devices

U26, U27, U28

DDR3 x40 memory

Three 128-MB DDR3A SDRAM with ECC, each with a 16-bit data bus

for a hard memory controller.

U8, U15, U22,

U30

DDR3 x64 memory

Four 128-MB DDR3B SDRAM, each with a 16-bit data bus for a soft

memory controller.

U20

Flash x16 memory

1-Gb synchronous flash devices with a 16-bit data bus for non-volatile

memory.

Communication Ports

J16

PCI Express edge connector

Gold-plated edge fingers connector for up to ×4 signaling in Gen1

mode.

J1, J2

HSMC port

Two ports, one with four transceiver channels and 84 CMOS or 17

LVDS channels as per the HSMC specification, and one with CMOS I/O

assignments and DQS/DQx32 assignments for future use.

J9

Gigabit Ethernet port

RJ-45 connector which provides a 10/100/1000 Ethernet connection

via a Marvell 88E1111 PHY and the FPGA-based Altera Triple Speed

Ethernet MegaCore function in RGMII mode.

Video and Display Ports

J10

Character LCD

Connector that interfaces to a provided 16 character × 2 line LCD

module along with four standoffs.

J11, J12

SDI video port

Two 75-

sub-miniature version B (SMB) connectors that provide a

full-duplex SDI interface through a LMH0303 cable driver and

LMH0384 cable equalizer. By default, this is not an active interface but

is only available when you switch the resistor placement. After making

this resistor change, the HSMC port A transceiver channel 3 is no

longer available.

Power Supply

J16

PCI Express edge connector

Interfaces to a PCI Express root port such as an appropriate PC

motherboard.

J8

DC input jack

Accepts a 19-V DC power supply. Do not use this input jack while the

board is plugged into a PCI Express slot.

Table 2–1. Board Components (Part 3 of 4)

Board Reference

Type

Description