2 gx1 module core clock, 3 internal fast-pci clock, Table 4-6 – AMD Geode SC1201 User Manual

Page 85: Core clock frequency, Table 4-7, Strapped core clock frequency

AMD Geode™ SC1200/SC1201 Processor Data Book

85

General Configuration Block

32579B

4.5.2

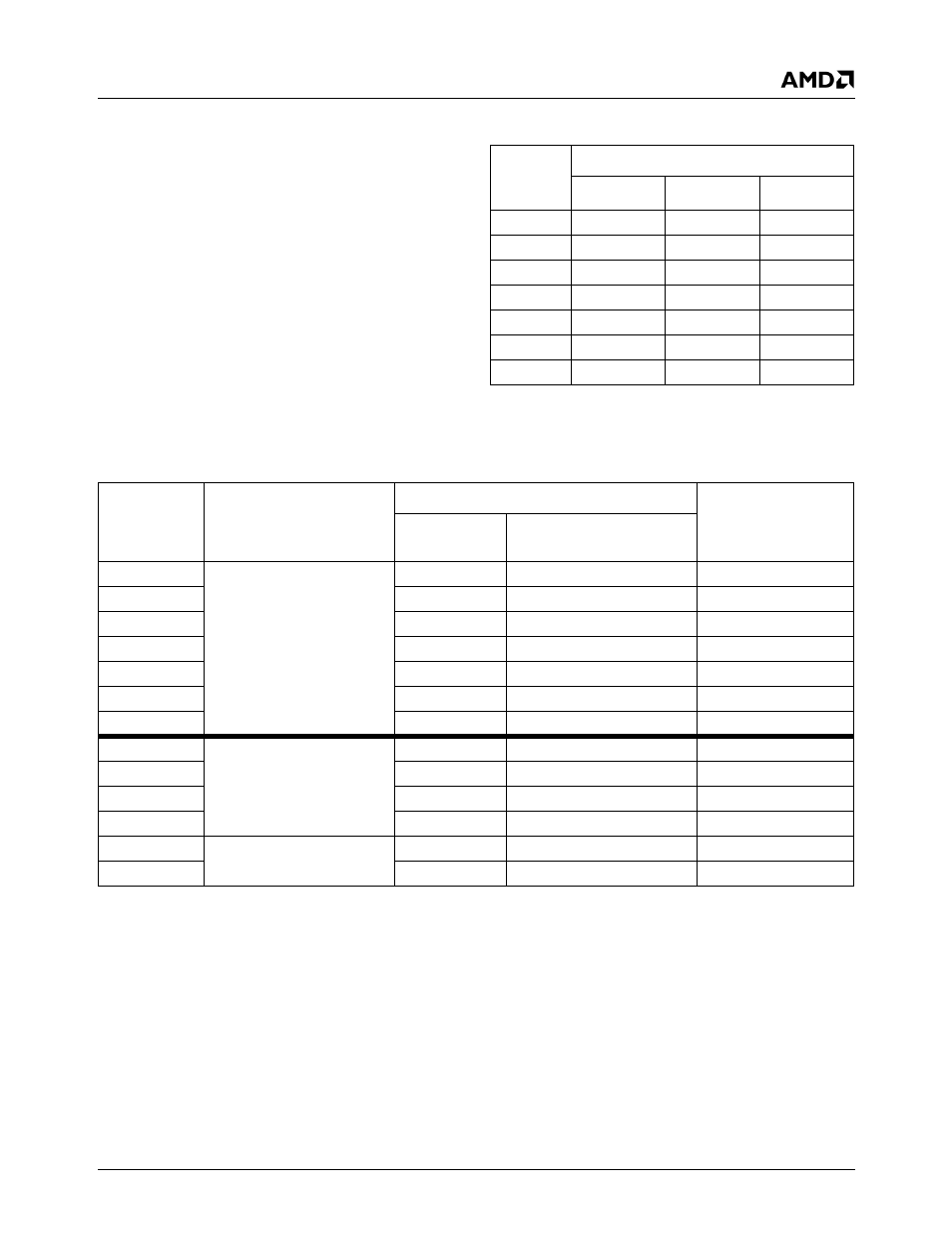

GX1 Module Core Clock

The core clock is generated by an Analog Delay Loop

(ADL) clock generator from the internal Fast-PCI clock. The

clock can be any whole number multiple of the input clock

between 4 and 10. Possible values are listed in Table 4-6.

At power-on reset, the core clock multiplier value is set

according to the value of four strapped balls - CLKSEL[3:0]

(balls P30, D29, AF3, B8). These balls also select the clock

which is used as input to the multiplier, as shown in Table

4-7.

4.5.3

Internal Fast-PCI Clock

The internal Fast-PCI clock can be configured to 33, 48, or

66 MHz via strap options on the CLKSEL1 and CLKSEL0

balls. These can be read in the internal Fast-PCI Clock field

in the CCFC register (GCB+I/O Offset 1Eh[9:8]). (See

Table 4-8 on page 87 details on the CCFC register.)

Note:

Not all speeds are supported. For information on supported speeds, see Section A.1 "Order Information" on page

441.

Table 4-6. Core Clock Frequency

ADL

Multiplier

Value

Internal Fast-PCI Clock Freq. (MHz)

33.33

48

66.67

4

133.3

192

266.7

5

166.7

240

---

6

200

288

---

7

233.3

---

---

8

266.7

---

---

9

---

---

---

10

---

---

---

Table 4-7. Strapped Core Clock Frequency

CLKSEL[3:0]

Straps

Internal Fast-PCI Clock

Freq. (MHz)

(GCB+I/O Offset 1Eh[9:8])

Default ADL Multiplier

Maximum Core

Clock Freq. (MHz)

Multiply By

Multiplier Value

(GCB+I/O Offset 1Eh[3:0])

0111

33.33

4

0100

133

1011

5

0101

167

1111

6

0110

200

0000

7

0111

233

0100

8

1000

266

1000

9

1001

Reserved

1100

10

1010

Reserved

0001

48

4

0100

192

0101

5

0101

240

1001

6

0110

288

1101

7 0111

Reserved

0110

66.67

4

0100

266

1010

5 0101

Reserved