AMD Geode SC1201 User Manual

Page 264

264

AMD Geode™ SC1200/SC1201 Processor Data Book

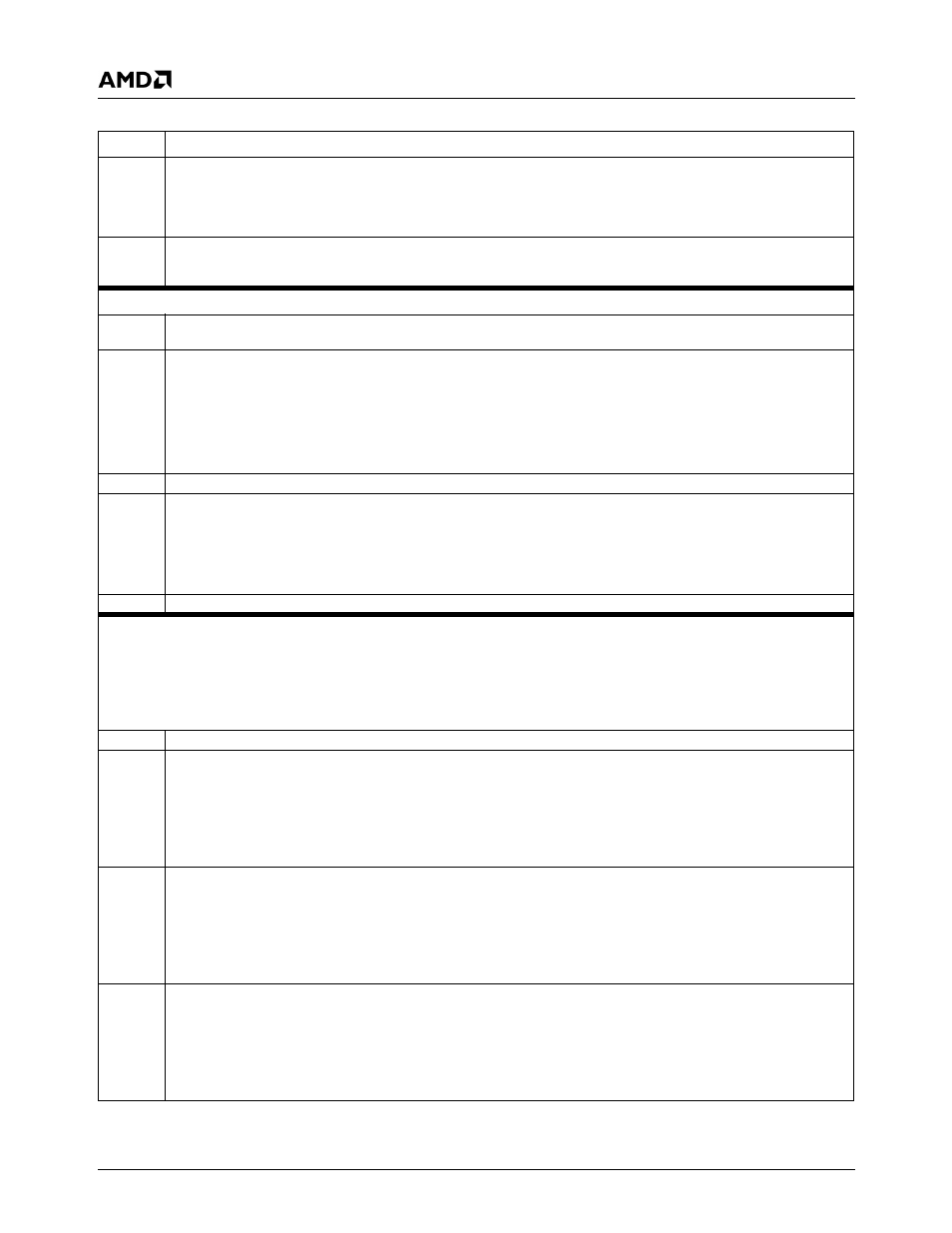

Core Logic Module - Audio Registers - Function 3

32579B

16

Codec Status Valid. (Read Only) Indicates if the status in bits [15:0] of this register is valid. This bit is high during slots 3 to

11 of the AC97 frame (i.e., for approximately 14.5 µs), for every frame.

0: No.

1: Yes.

15:0

Codec Status. (Read Only) This is the codec status data that is received from the codec in slot 2 on SDATA_IN. Only bits

[19:4] are used from slot 2. If this register is read with both bits 16 and 17 of this register set to 1, this field is updated in the

current AC97 frame, and codec status data is valid. This bit field is updated only if the codec sent status data.

Offset 0Ch-0Fh

Codec Command Register (R/W)

Reset Value: 00000000h

31:24

Codec Command Address. Address of the codec control register for which the command is being sent. This address goes

in slot 1 bits [19:12] on SDATA_OUT.

23:22

Codec Communication. Indicates the codec that the Core Logic module is communicating with.

00: Primary codec

01: Secondary codec

10: Third codec

11: Fourth codec

Only 00 and 01 are valid settings for this bit field.

21:17

Reserved. Must be set to 0.

16

Codec Command Valid. (Read Only) Indicates if the command in bits [15:0] of this register is valid.

0: No.

1: Yes.

This bit is set by hardware when a codec command is written to the Codec Command register. It remains set until the com-

mand has been sent to the codec.

15:0

Codec Command. This is the command being sent to the codec in bits [19:4] of slot 2 on SDATA_OUT.

Offset 10h-11h

Second Level Audio SMI Status Register (RC)

Reset Value: 0000h

The bits in this register contain second level SMI status reporting. Top level is reported at F1BAR0+I/O Offset 00h/02h[1]. Reading this

register clears the status bits at both the second and top levels. Note that bit 0 has a third level of status reporting which also must be

"read to clear".

A read-only “Mirror” version of this register exists at F3BAR0+I/O Memory Offset 12h. If the value of the register must be read without

clearing the SMI source (and consequently de-asserting SMI), F3BAR0+Memory Offset 12h can be read instead.

15:8

Reserved. Must be set to 0.

7

Audio Bus Master 5 SMI Status. Indicates if an SMI was caused by an event occurring on Audio Bus Master 5.

0: No.

1: Yes.

SMI generation is enabled when Audio Bus Master 5 is enabled (F3BAR0+Memory Offset 48h[0] = 1).

An SMI is then generated when the End of Page bit is set in the Audio Bus Master 5 SMI Status Register (F3BAR0+Memory

Offset 49h[0] = 1).

6

Audio Bus Master 4 SMI Status. Indicates if an SMI was caused by an event occurring on Audio Bus Master 4.

0: No.

1: Yes.

SMI generation is enabled when Audio Bus Master 4 is enabled (F3BAR0+Memory Offset 40h[0] = 1).

An SMI is then generated when the End of Page bit is set in the Audio Bus Master 4 SMI Status Register (F3BAR0+Memory

Offset 41h[0] = 1).

5

Audio Bus Master 3 SMI Status. Indicates if an SMI was caused by an event occurring on Audio Bus Master 3.

0: No.

1: Yes.

SMI generation is enabled when Audio Bus Master 3 is enabled (F3BAR0+Memory Offset 38h[0] = 1).

An SMI is then generated when the End of Page bit is set in the Audio Bus Master 3 SMI Status Register (F3BAR0+Memory

Offset 39h[0] = 1).

Table 6-38. F3BAR0+Memory Offset: Audio Configuration Registers (Continued)

Bit

Description