Table 5-56, Bank 1 bit map, Table 5-57 – AMD Geode SC1201 User Manual

Page 139: Bank 2 bit map, Table 5-58, Bank 3 bit map, Table 5-59, Bank 4 bit map

AMD Geode™ SC1200/SC1201 Processor Data Book

139

SuperI/O Module

32579B

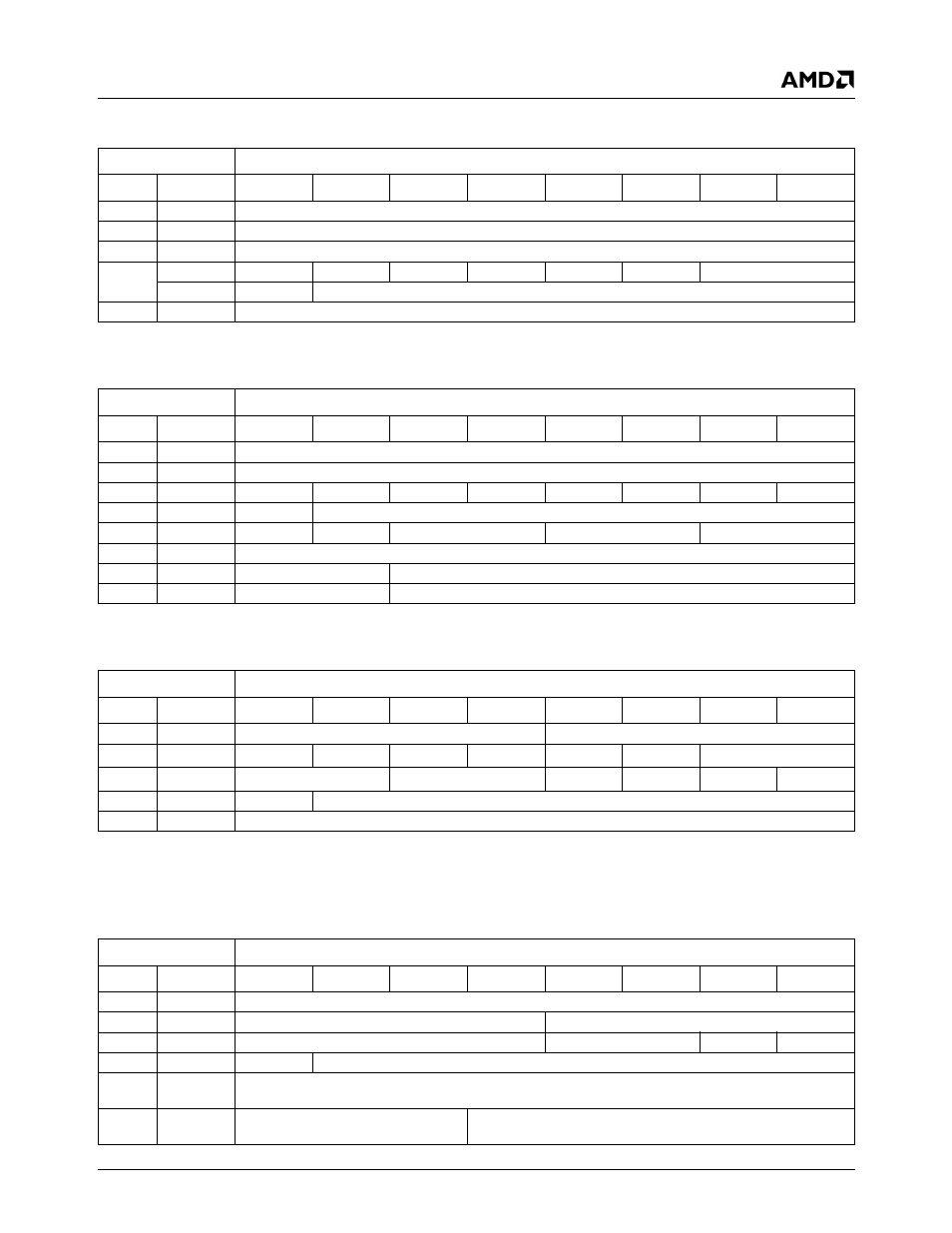

Table 5-56. Bank 1 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

LBGD(L)

LBGD[7:0] (Low Byte Data)

01h

LBGD(H)

LBGD[15:8] (High Byte Data)

02h

RSVD

RSVD

03h

LCR

BKSE

SBRK

STKP

EPS

PEN

STB

WLS[1:0]

BSR

BKSE

BSR[6:0] (Bank Select)

04h-07h

RSVD

RSVD

Table 5-57. Bank 2 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

BGD(L)

BGD[7:0] (Low Byte Data)

01h

BGD(H)

BGD[15:8] (High Byte Data)

02h

EXCR1

BTEST

RSVD

ETDLBK

LOOP

DMASWP

DMATH

DMANF

EXT_SL

03h

BSR

BKSE

BSR[6:0] (Bank Select)

04h

EXCR2

LOCK

RSVD

PRESL[1:0]

RF_SIZ[1:0]

TF_SIZ[1:0]

05h

RSVD

RSVD

06h

TXFLV

RSVD

TFL[5:0]

07h

RXFLV

RSVD

RFL[5:0]

Table 5-58. Bank 3 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

MID

MID[3:0]

RID[3:0]

01h

SH_LCR

1

RSVD

SBRK

STKP

EPS

PEN

STB

WLS[1:0]

02h

SH_FCR

2

RXFTH[1:0]

TXFTH[1:0]

RSVD

TXSR

RXSR

FIFO_EN

03h

BSR

BKSE

BSR[6:0] (Bank Select)

04h-07h

RSVD

Reserved

1.

LCR Register Value

2.

FCR Register Value

Table 5-59. Bank 4 Bit Map

Register

Bits

Offset

Name

7

6

5

4

3

2

1

0

00h

TMR(L)

TMR[7:0] (Low Byte Data)

01h

TMR(H)

RSVD

TMR[11:8] (High Byte Data)

02h

IRCR1

RSVD

IR_SL[1:0]

CTEST

TMR_EN

03h

BSR

BKSE

BSR[6:0] (Bank Select)

04h

TFRL(L)/

TFRCC(L)

TFRL[7:0] / TFRCC[7:0] (Low Byte Data)

05h

TFRL(H)/

TFRCC(H)

RSVD

TFRL[12:8] / TFRCC[12:8] (High Byte Data)