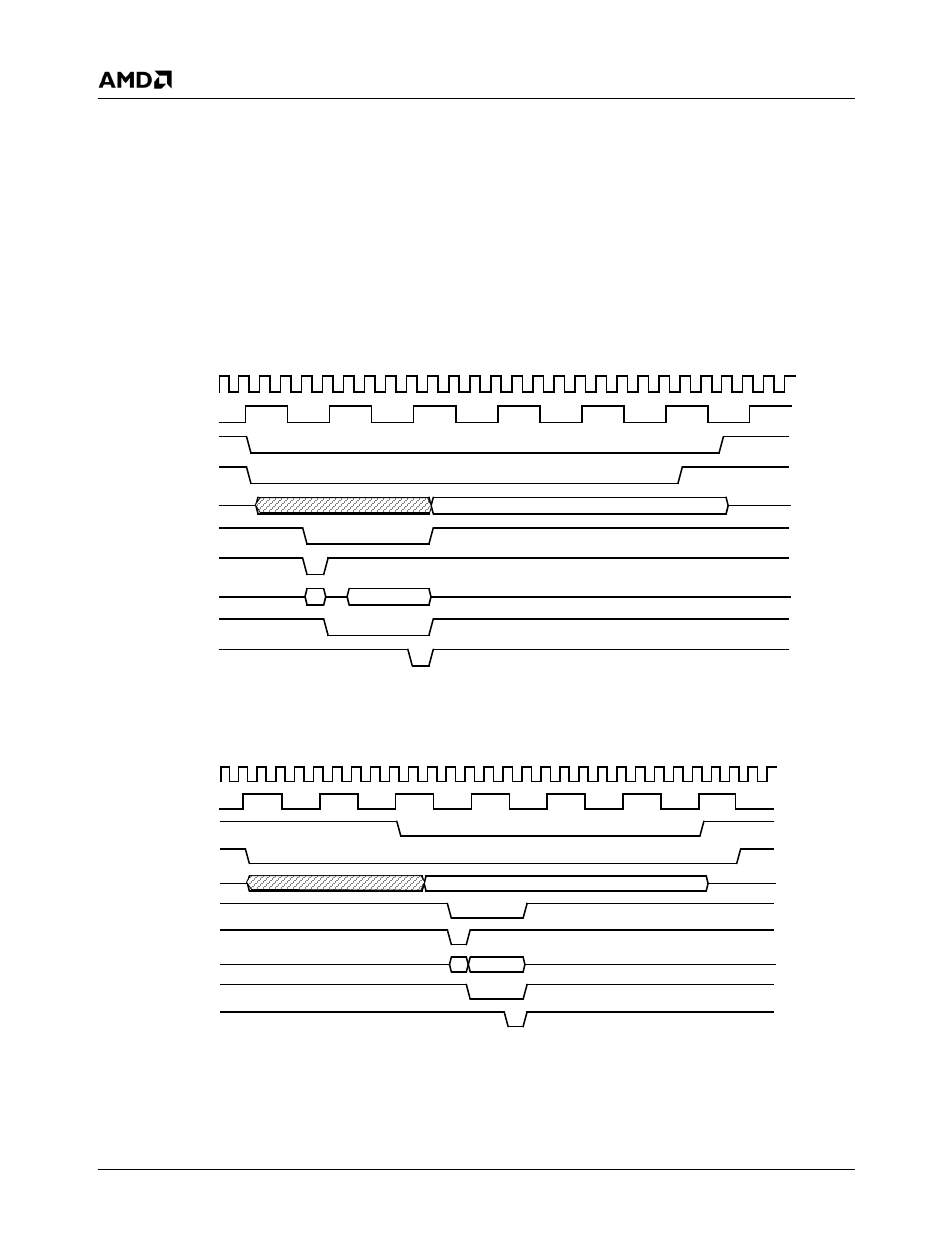

5 isa dma, Figure 6-4, Isa dma read from pci memory – AMD Geode SC1201 User Manual

Page 150: Figure 6-5, Isa dma write to pci memory

150

AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module

32579B

6.2.5.5

ISA DMA

DMA transfers occur between ISA I/O peripherals and sys-

tem memory (i.e., not available externally). The data width

can be either 8 or 16 bits. Out of the seven DMA channels

available, four are used for 8-bit transfers while the remain-

ing three are used for 16-bit transfers. One byte or WORD

is transferred in each DMA cycle.

Note:

The Core Logic module does not support DMA

transfers to ISA memory.

The ISA DMA device initiates a DMA request by asserting

one of the DRQ[7:5, 3:0] signals. When the Core Logic

module receives this request, it sends a bus grant request

to the PCI arbiter. After the PCI bus has been granted, the

respective DACK# is driven active.

The Core Logic module generates PCI memory read or

write cycles in response to a DMA cycle. Figure 6-4 and

Figure 6-5 are examples of DMA memory read and mem-

ory write cycles. Upon detection of the DMA controller’s

MEMR# or MEMW# active, the Core Logic module starts

the PCI cycle, asserts FRAME#, and negates an internal

IOCHRDY. This assures the DMA cycle does not complete

before the PCI cycle has provided or accepted the data.

IOCHRDY is internally asserted when IRDY# and TRDY#

are sampled active.

Figure 6-4. ISA DMA Read from PCI Memory

Figure 6-5. ISA DMA Write to PCI Memory

PCICLK

ISACLK

MEMR#

IOW#

FRAME#

AD[31:0]

IRDY#

TRDY#

SD[15:0]

IOCHRDY

PCICLK

ISACLK

MEMW#

IOR#

FRAME#

AD[31:0]

IRDY#

TRDY#

SD[15:0]

IOCHRDY