AMD Geode SC1201 User Manual

Page 209

AMD Geode™ SC1200/SC1201 Processor Data Book

209

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32579B

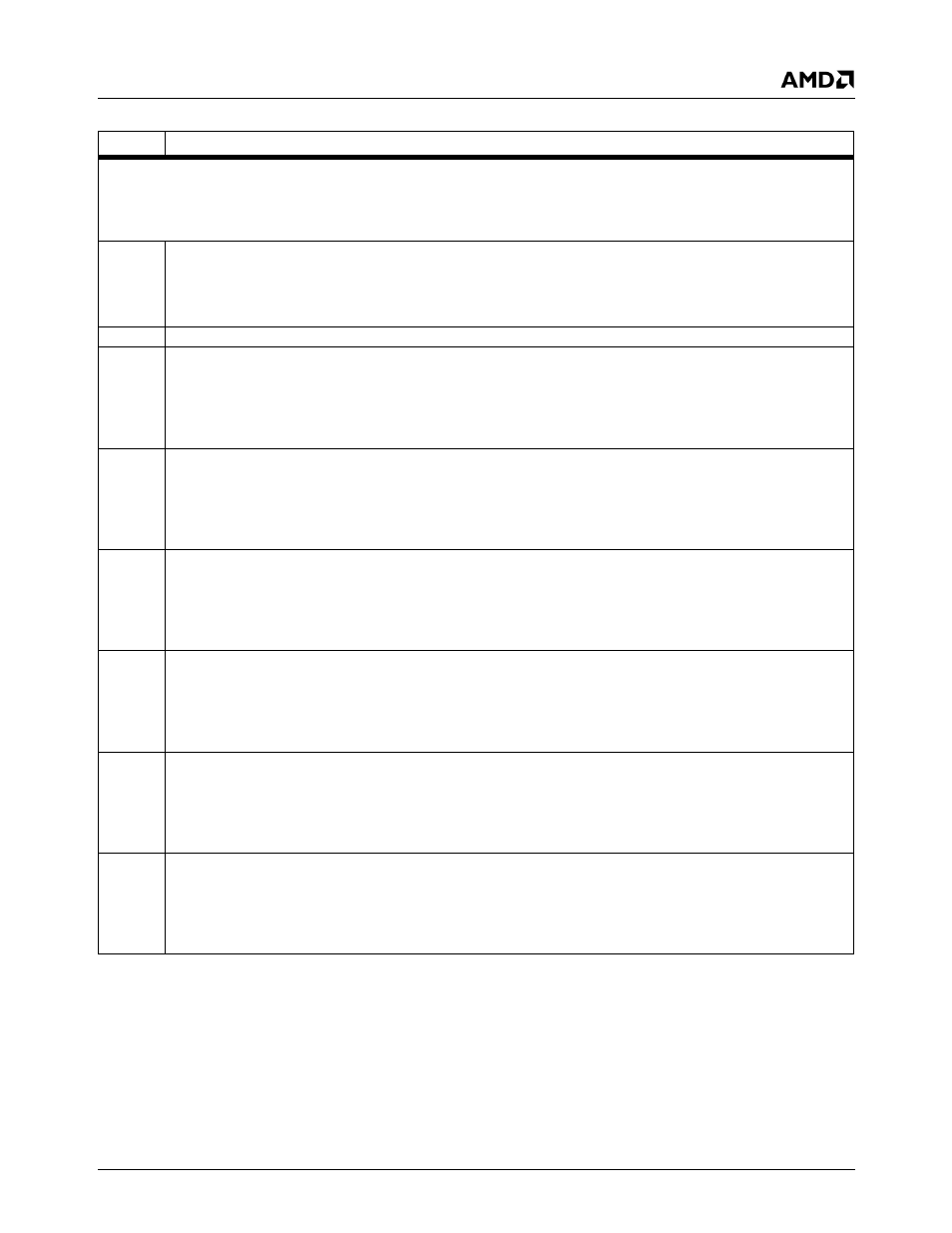

Index 86h

Second Level PME/SMI Status Mirror Register 3 (RO)

Reset Value: 00h

The bits in this register contain second level status reporting. Top level status is reported in F1BAR0+I/O Offset 00h/02h[0].

This register is called a “Mirror” register since an identical register exists at F0 Index F6h. Reading this register does not clear the status,

while reading its counterpart at F0 Index F6h clears the status at both the second and top levels.

7

Video Access Trap SMI Status. Indicates whether or not an SMI was caused by a trapped I/O access to the Video I/O Trap.

0: No.

1: Yes.

To enable SMI generation, set F0 Index 82h[7] to 1.

6

Reserved.

5

Secondary Hard Disk Access Trap SMI Status. Indicates whether or not an SMI was caused by a trapped I/O access to

the secondary hard disk.

0: No.

1: Yes.

To enable SMI generation, set F0 Index 83h[6] to 1.

4

Secondary Hard Disk Idle Timer SMI Status. Indicates whether or not an SMI was caused by expiration of Secondary

Hard Disk Idle Timer Count register (F0 Index ACh).

0: No.

1: Yes.

To enable SMI generation, set F0 Index 83h[7] to 1.

3

Keyboard/Mouse Access Trap SMI Status. Indicates whether or not an SMI was caused by an trapped I/O access to the

keyboard or mouse.

0: No.

1: Yes.

To enable SMI generation, set F0 Index 82h[3] to 1.

2

Parallel/Serial Access Trap SMI Status. Indicates whether or not an SMI was caused by a trapped I/O access to either the

serial or parallel ports.

0: No.

1: Yes.

To enable SMI generation, set F0 Index 82h[2] to 1.

1

Floppy Disk Access Trap SMI Status. Indicates whether or not an SMI was caused by a trapped I/O access to the floppy

disk.

0: No.

1: Yes.

To enable SMI generation, set F0 Index 82h[1] to 1.

0

Primary Hard Disk Access Trap SMI Status. Indicates whether or not an SMI was caused by a trapped I/O access to the

primary hard disk.

0: No.

1: Yes.

To enable SMI generation, set F0 Index 82h[0] to 1.

Table 6-29. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support (Continued)

Bit

Description