1 sub-isa bus cycles, 2 sub-isa support of delayed pci transactions, Figure 6-2 – AMD Geode SC1201 User Manual

Page 148: Non-posted fast-pci to isa access

148

AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module

32579B

6.2.5.1

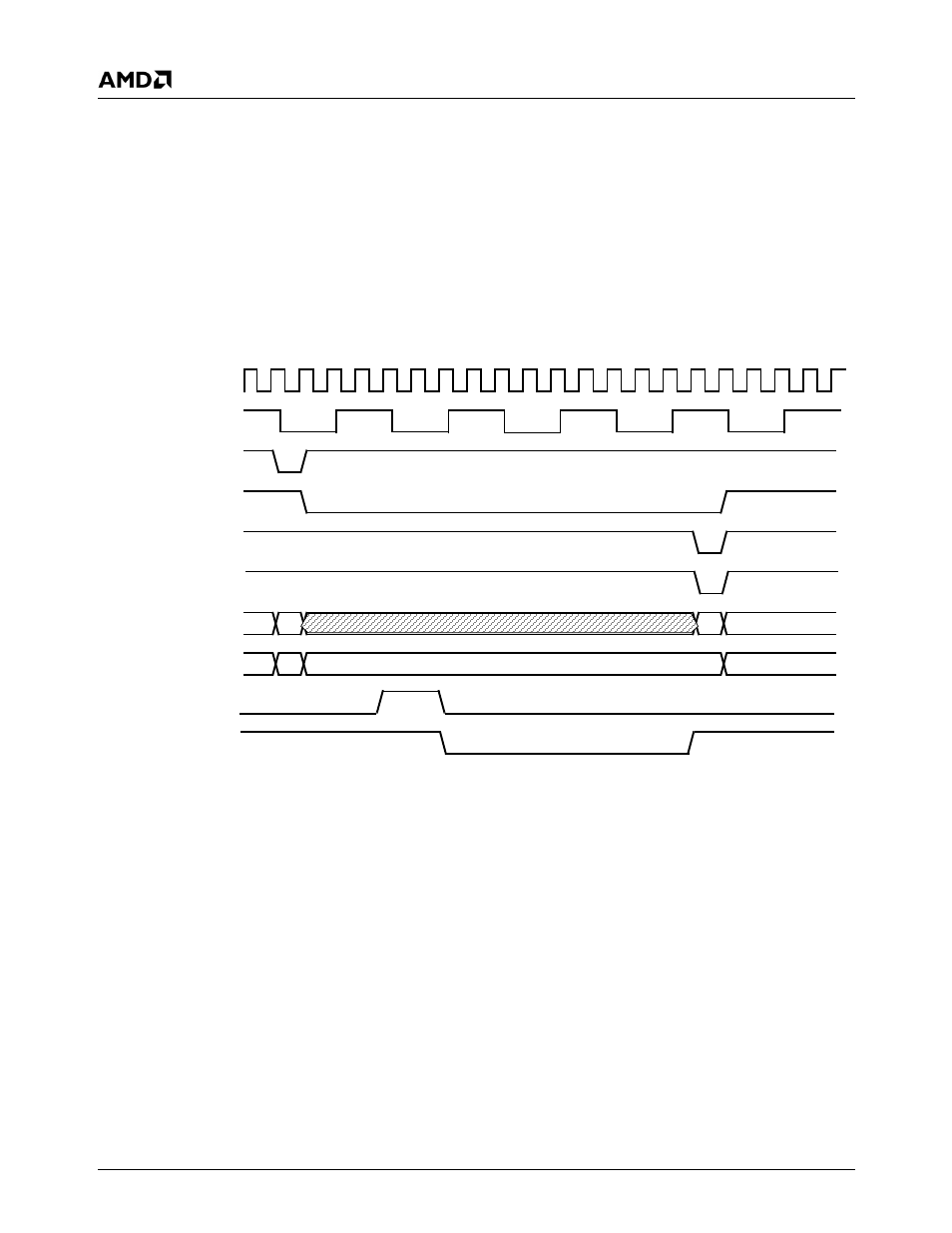

Sub-ISA Bus Cycles

The ISA bus controller issues multiple ISA cycles to satisfy

PCI transactions that are larger than 16 bits. A full 32-bit

read or write results in two 16-bit ISA transactions or four 8-

bit ISA transactions. The ISA controller gathers the data

from multiple ISA read cycles and returns TRDY# to the

PCI bus.

SA[23:0] are a concatenation of ISA LA[23:17] and

SA[19:0] and perform equivalent functionality at a reduced

pin count.

Figure 6-2 shows the relationship between a PCI cycle and

the corresponding ISA cycle generated.

Note:

Not all signals described in Figure 6-2 are available

externally. See Section 3.4.8 "Sub-ISA Interface

Signals" on page 59 for more information about

which Sub-ISA signals are externally available on

the SC1200/SC1201 processor.

6.2.5.2

Sub-ISA Support of Delayed PCI Transactions

Multiple PCI cycles occur for every slower ISA cycle. This

prevents slow PCI cycles from occupying too much band-

width and allows access to other PCI traffic. Figure 6-3 on

page 149 shows the relationship of PCI cycles to an ISA

cycle with PCI delayed transactions enabled.

Figure 6-2. Non-Posted Fast-PCI to ISA Access

Fast-PCI_CLK

ISACLK

FRAME#

IRDY#

TRDY#

AD[31:0] (Read)

RD#,WR#,IOR#,IOW#

AD[31:0] (Write)

BALE

STOP#

MEMR#,MEMW#