AMD Geode SC1201 User Manual

Page 254

254

AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module - SMI Status and ACPI Registers - Function 1

32579B

5

GPWIO_SMIEN1. Allow GPWIO1 to generate an SMI.

0: Disable. (Default)

1: Enable.

See F1BAR1+I/O Offset 07h[3] for debounce information.

Bit 1 of this register must be set to 0 (input) for GPWIO1 to be able to generate an SMI.

If asserted, this bit overrides the setting of F1BAR1+I/O Offset 12h[9] and its status is reported in F1BAR0+I/O Offset 00h/

02h[0].

4

GPWIO_SMIEN0. Allow GPWIO0 to generate an SMI.

0: Disable. (Default)

1: Enable.

See F1BAR1+I/O Offset 07h[3] for debounce information.

Bit 0 of this register must be set to 0 (input) for GPWIO0 to be able to generate an SMI.

If enabled, this bit overrides the setting of F1BAR1+I/O Offset 12h[8] and its status is reported in F1BAR0+I/O Offset 00h/

02h[0].

3

Reserved.

2

GPWIO2_DIR. Selects the direction of GPWIO2.

0: Input.

1: Output.

1

GPWIO1_DIR. Selects the direction of GPWIO1.

0: Input.

1: Output.

0

GPWIO0_DIR. Selects the direction of the GPWIO0.

0: Input.

1: Output.

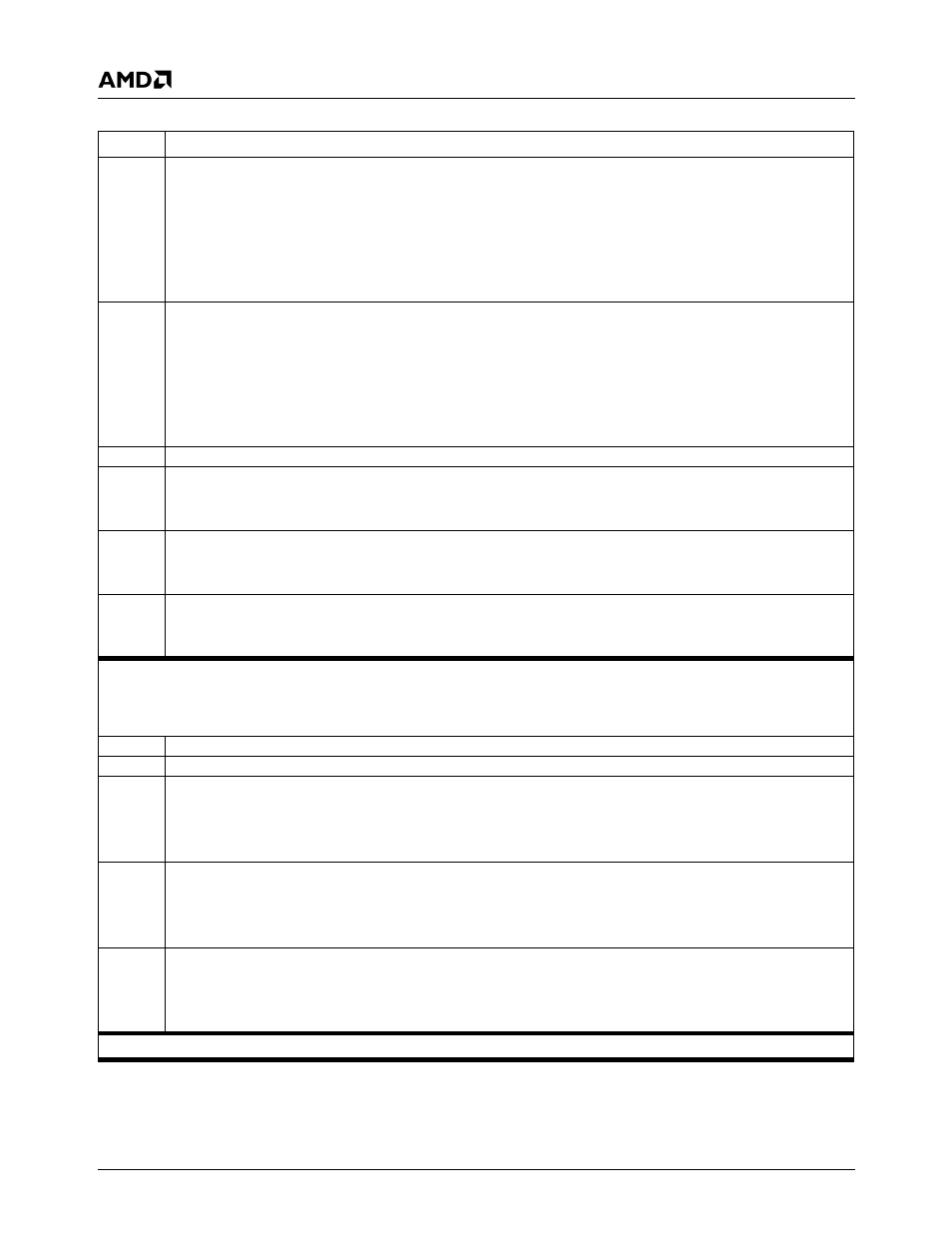

Offset 16h

GPWIO Data Register (R/W)

Reset Value: 00h

This register contains the direct values of the GPWIO2-GPWIO0 pins. Write operations are valid only for bits defined as outputs. Reads

from this register read the last written value if the pin is an output. The pins are configured as inputs or outputs in F1BAR1+I/O Offset

15h.

7:4

Reserved. Must be set to 0.

3

Reserved.

2

GPWIO2_DATA. Reflects the level of GPWIO2.

0: Low.

1: High.

A fixed high-to-low or low-to-high transition (debounce period) of 31 µs exists in order for GPWIO2 to be recognized.

1

GPWIO1_DATA. Reflects the level of GPWIO1.

0: Low.

1: High.

See F1BAR1+I/O Offset 07h[3] for debounce information.

0

GPWIO0_DATA. Reflects the level of GPWIO0.

0: Low.

1: High.

See F1BAR1+I/O Offset 07h[3] for debounce information.

Offset 17h

Reserved

Reset Value: 00h

Table 6-34. F1BAR1+I/O Offset: ACPI Support Registers (Continued)

Bit

Description