Table 4-4, High-resolution timer registers – AMD Geode SC1201 User Manual

Page 82

82

AMD Geode™ SC1200/SC1201 Processor Data Book

General Configuration Block

32579B

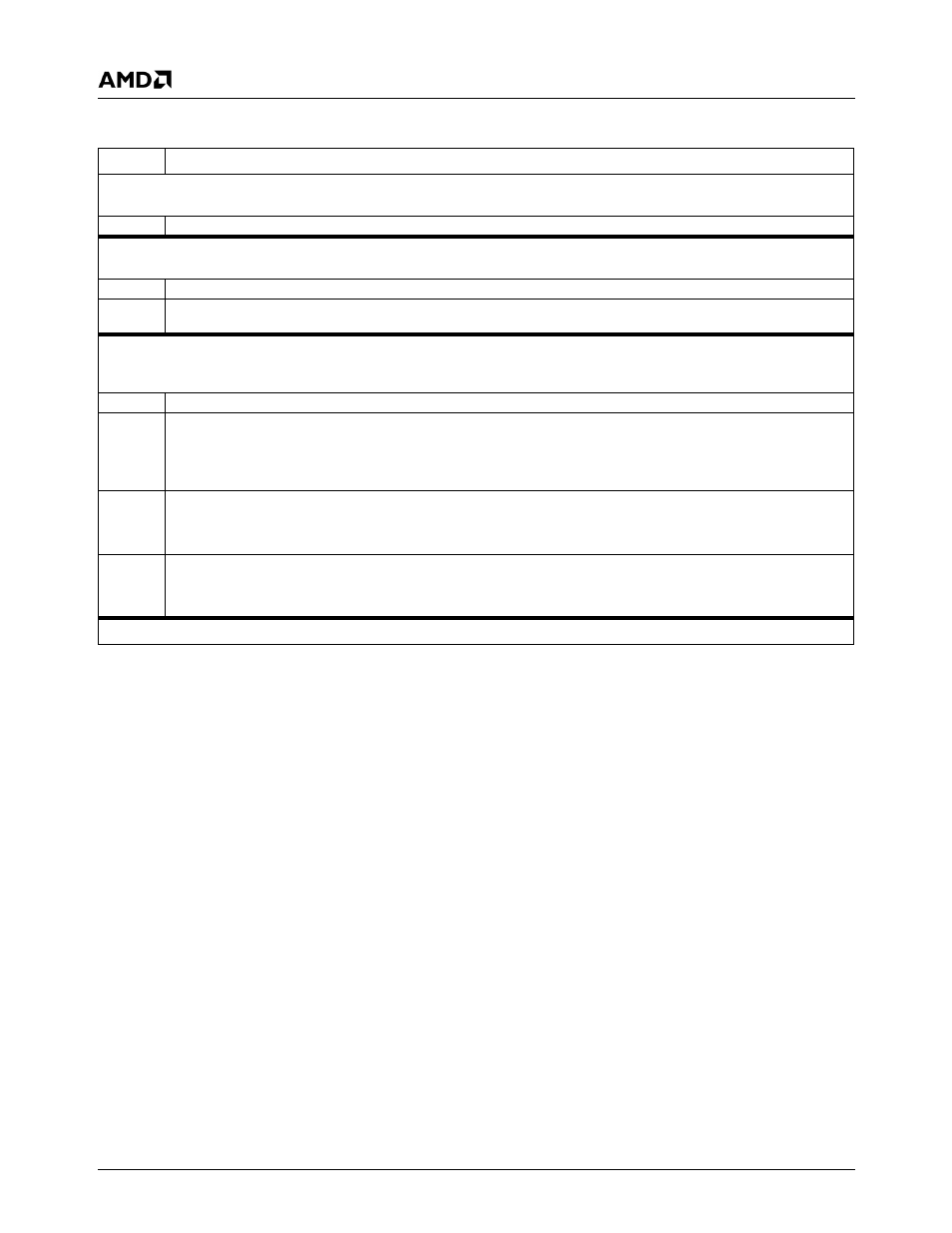

Table 4-4. High-Resolution Timer Registers

Bit

Description

Offset 08h-0Bh

TIMER Value Register - TMVALUE (RO)

Reset Value: xxxxxxxxh

This register contains the current value of the High-Resolution Timer.

31:0

Current Timer Value.

Offset 0Ch

TIMER Status Register - TMSTS (R/W)

Reset Value: 00h

This register supplies the High-Resolution Timer status information.

7:1

Reserved.

0

TMSTS (TIMER Status). This bit is set to 1 when the most significant bit (bit 31) of the timer changes from 1 to 0. It is

cleared to 0 upon system reset or when 1 is written by software to this bit.

Offset 0Dh

TIMER Configuration Register - TMCNFG (R/W)

Reset Value: 00h

This register enables the High-Resolution Timer interrupt; selects the Timer clock; and disables the 27 MHz internal clock during low

power states.

7:3

Reserved.

2

TM27MPD (TIMER 27 MHz Power Down). This bit is cleared to 0 when POR# is asserted or when the GX1 module de-

asserts its internal SUSPA# signal (i.e., on SUSPA# rising edge). See Section 4.4.2.1 "Usage Hints" on page 81.

0: 27 MHz input clock is enabled.

1: 27 MHz input clock is disabled when the GX1 module asserts its internal SUSPA# signal.

1

TMCLKSEL (TIMER Clock Select).

0: Count-up timer uses the oscillator clock divided by 27.

1: Count-up timer uses the oscillator clock, 27 MHz clock.

0

TMEN (TIMER Interrupt Enable).

0: High-Resolution Timer interrupt is disabled.

1: High-Resolution Timer interrupt is enabled.

Offset 0Eh-0Fh

Reserved - RSVD