Table 6-47, Keyboard controller registers, S (table 6-47) – AMD Geode SC1201 User Manual

Page 307

AMD Geode™ SC1200/SC1201 Processor Data Book

307

Core Logic Module - ISA Legacy Register Space

32579B

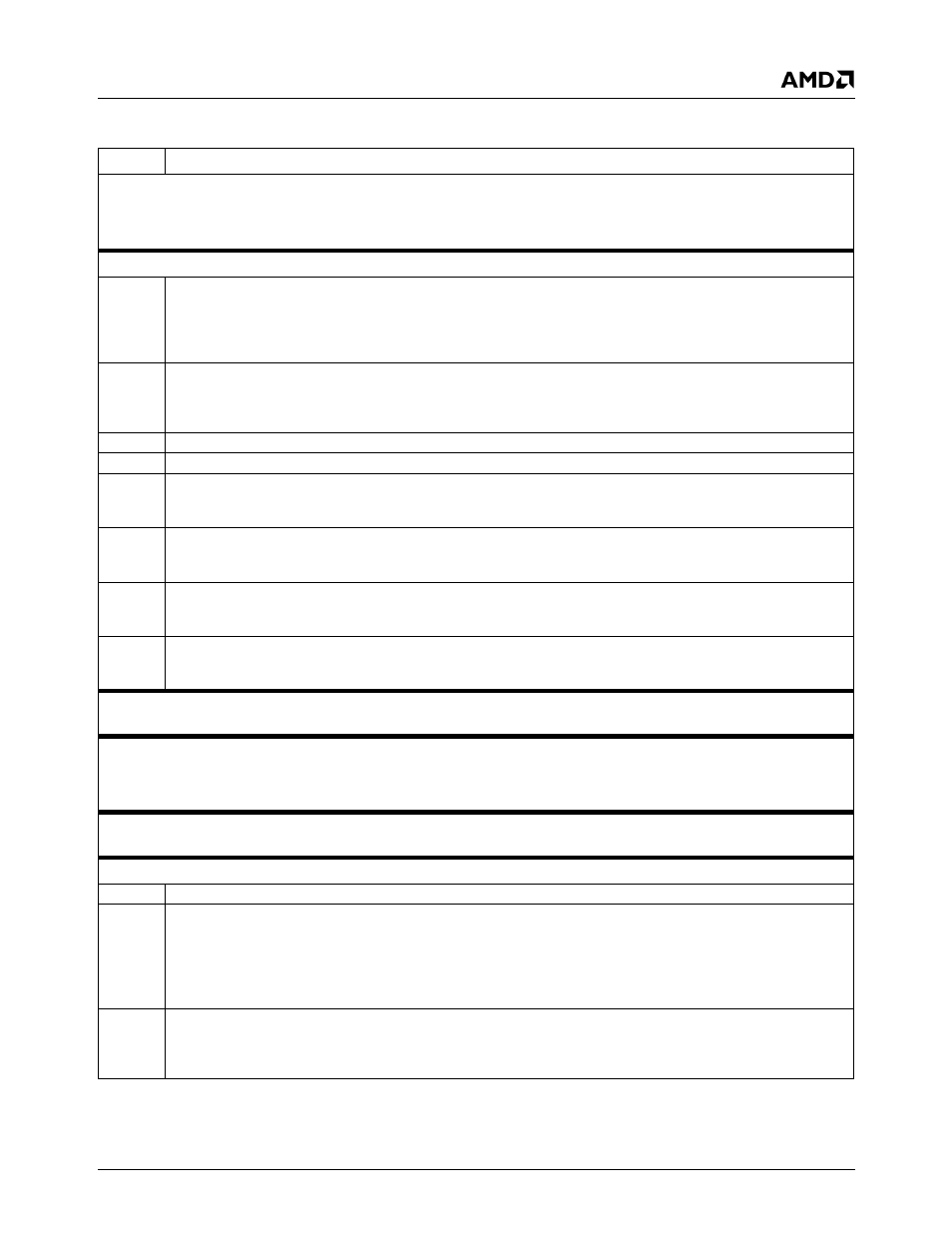

Table 6-47. Keyboard Controller Registers

Bit

Description

I/O Port 060h

External Keyboard Controller Data Register (R/W)

Keyboard Controller Data Register. All accesses to this port are passed to the ISA bus. If the fast keyboard gate A20 and reset fea-

tures are enabled through bit 7 of the ROM/AT Logic Control Register (F0 Index 52h[7]), the respective sequences of writes to this port

assert the A20M# signal or cause a warm CPU reset.

I/O Port 061h

Port B Control Register (R/W)

Reset Value: 00x01100b

7

PERR#/SERR# Status. (Read Only) Indicates if a PCI bus error (PERR#/SERR#) was asserted by a PCI device or by the

SC1200/SC1201 processor.

0: No.

1: Yes.

This bit can only be set if ERR_EN (bit 2) is set 0. This bit is set 0 after a write to ERR_EN with a 1 or after reset.

6

IOCHK# Status. (Read Only) Indicates if an I/O device is reporting an error to the SC1200/SC1201 processor.

0: No.

1: Yes.

This bit can only be set if IOCHK_EN (bit 3) is set 0. This bit is set 0 after a write to IOCHK_EN with a 1 or after reset.

5

PIT OUT2 State. (Read Only) This bit reflects the current status of the of the PIT Counter 2 (OUT2).

4

Toggle. (Read Only) This bit toggles on every falling edge of Counter 1 (OUT1).

3

IOCHK# Enable.

0: Generates an NMI if IOCHK# is driven low by an I/O device to report an error. Note that NMI is under SMI control.

1: Ignores the IOCHK# input signal and does not generate NMI.

2

PERR/ SERR Enable. Generate an NMI if PERR#/SERR# is driven active to report an error.

0: Enable.

1: Disable.

1

PIT Counter2 (SPKR).

0: Forces Counter 2 output (OUT2) to zero.

1: Allows Counter 2 output (OUT2) to pass to the speaker.

0

PIT Counter2 Enable.

0: Sets GATE2 input low.

1: Sets GATE2 input high.

I/O Port 062h

External Keyboard Controller Mailbox Register (R/W)

Keyboard Controller Mailbox Register.

I/O Port 064h

External Keyboard Controller Command Register (R/W)

Keyboard Controller Command Register. All accesses to this port are passed to the ISA bus. If the fast keyboard gate A20 and reset

features are enabled through bit 7 of the ROM/AT Logic Control Register (F0 Index 52h[7]), the respective sequences of writes to this

port assert the A20M# signal or cause a warm CPU reset.

I/O Port 066h

External Keyboard Controller Mailbox Register (R/W)

Keyboard Controller Mailbox Register.

I/O Port 092h

Port A Control Register (R/W)

Reset Value: 02h

7:2

Reserved. Must be set to 0.

1

A20M# Assertion. Assert A20# (internally).

0: Enable.

1: Disable.

This bit reflects A20# status and can be changed by keyboard command monitoring.

An SMI event is generated when this bit is changed, if enabled by F0 index 53h[0]. The SMI status is reported in F1BAR0+I/

O Offset 00h/02h[7].

0

Fast CPU Reset. WM_RST SMI is asserted to the BIOS.

0: Disable.

1: Enable.

This bit must be cleared before the generation of another reset.